1/fゆらぎをHDLにしてみた [FPGA]

前回、間欠カオス法を整数化したので最低限度の18bit精度ででHDLしてみた(というか、正確にはHDL化を前提に必要ビット数を見積もっていたのだけども)。

それで結論から先に言うと、どうやら18bit精度だと特定の値で繰り返しパターンに入ってしまうようだ。

これが実際にHDL実装したもののSignalTapで観測した様子。

綺麗に繰り返しパターンにはまってしまっててどうしたものかと考えていたところ、そもそもカオス系なんだから、フィードバックにちょっとだけノイズを混ぜてやれば安定系から崩れるのでは?と思い、2乗の値を加算する部分でLSBの1ビットだけランダムにひっくり返す処理を追加してみた。

と、こう書くとややこしい処理をいれたなと思われそうだけども、やってることはXorshit32の適当なビット(今回はMSBを使った)でフィードバックのLSBにXORをかけただけ。

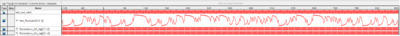

結果はこう。

綺麗にカオス挙動に戻った。

ついでなので、乗算器を使ってないタイミングでランダム値の2乗計算を行って、rand値、rand^2値、1/f値を同時に取得できるように修正。

これで実装ロジック数は120LE+2DSPとかなりコンパクトになっている。

PWMでLEDをチカチカさせるとこんな感じ

それで結論から先に言うと、どうやら18bit精度だと特定の値で繰り返しパターンに入ってしまうようだ。

これが実際にHDL実装したもののSignalTapで観測した様子。

綺麗に繰り返しパターンにはまってしまっててどうしたものかと考えていたところ、そもそもカオス系なんだから、フィードバックにちょっとだけノイズを混ぜてやれば安定系から崩れるのでは?と思い、2乗の値を加算する部分でLSBの1ビットだけランダムにひっくり返す処理を追加してみた。

と、こう書くとややこしい処理をいれたなと思われそうだけども、やってることはXorshit32の適当なビット(今回はMSBを使った)でフィードバックのLSBにXORをかけただけ。

結果はこう。

綺麗にカオス挙動に戻った。

ついでなので、乗算器を使ってないタイミングでランダム値の2乗計算を行って、rand値、rand^2値、1/f値を同時に取得できるように修正。

これで実装ロジック数は120LE+2DSPとかなりコンパクトになっている。

PWMでLEDをチカチカさせるとこんな感じ

s_osafunePWMでLチカさせてみた。ノイズ発生器部分で120LE+2DSP https://t.co/exjEgt350O06/08 23:24

2019-06-08 23:53