CH552EでUSB-Blasterクローン [FPGA]

CH552シリーズはUSBペリフェラルを内蔵した格安マイコンで、廉価ボードでUSBデバッグインターフェースとして使われているのを見かけます。

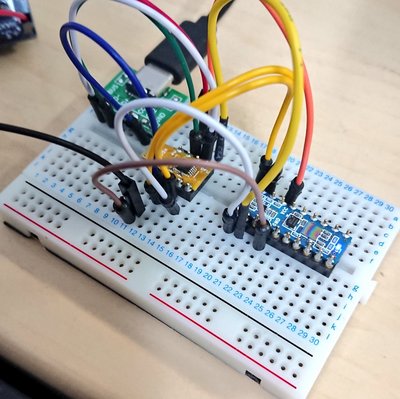

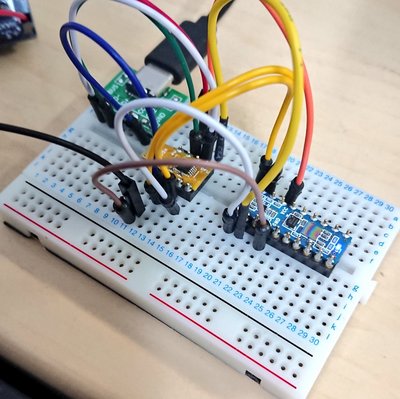

そんな中でUSB-Blasterクローンを作ってるリポジトリを見つけたので、CH552Eブレークアウトを使ってUSB-Blasterクローンを作ってみました。

元のリポジトリはこちら。

→ CH55x-USB-Blaster

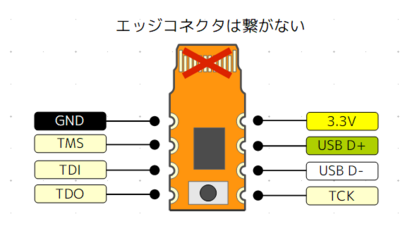

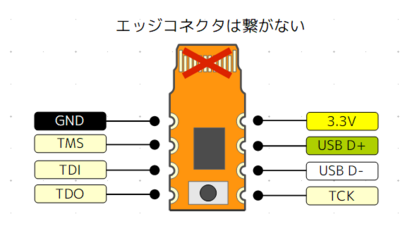

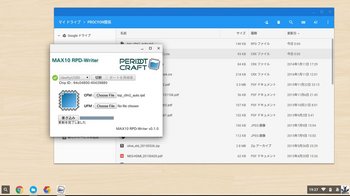

この中のRelese V0.1のHEXバイナリがCH552Eでそのまま使えます。Releaseに含まれるHEXをWCHISP Studioで書き込むと、以下のピンアサインでUSB-Blasterクローンとして動作します。

注意点はCH552EブレークアウトボードのI/Oを3.3Vで動作させるために、エッジコネクタのType-Cを使ってはならないことです。必ず外部にUSBコネクタを用意して、独立した(あるいはLDOで降圧した)3.3VをVUSB端子に供給します。

間違えてエッジコネクタに接続するとJTAGラインに5Vが印可されてしまうのでFPGAが破損します。HEXを書き込む際にも注意が必要です。

3.3V駆動なのでMAX10やCyclone10LPでもレベル変換なしでそのまま接続できます。

MCUが16MHz動作でPIOを直接操作しているため、速度としては数Mbps程度でそれほど高速ではありません。速度も純正のUSB-Blasterに比べて1/2~1/4といったところですが、NiosII dgbやSignalTapIIといったデバッグファンクションもきちんと動作します。

VID/PIDの問題があるので個人使用に留めておくべきですが、ローコストに出来るので趣味用途には十分でしょう。

そんな中でUSB-Blasterクローンを作ってるリポジトリを見つけたので、CH552Eブレークアウトを使ってUSB-Blasterクローンを作ってみました。

元のリポジトリはこちら。

→ CH55x-USB-Blaster

この中のRelese V0.1のHEXバイナリがCH552Eでそのまま使えます。Releaseに含まれるHEXをWCHISP Studioで書き込むと、以下のピンアサインでUSB-Blasterクローンとして動作します。

注意点はCH552EブレークアウトボードのI/Oを3.3Vで動作させるために、エッジコネクタのType-Cを使ってはならないことです。必ず外部にUSBコネクタを用意して、独立した(あるいはLDOで降圧した)3.3VをVUSB端子に供給します。

間違えてエッジコネクタに接続するとJTAGラインに5Vが印可されてしまうのでFPGAが破損します。HEXを書き込む際にも注意が必要です。

3.3V駆動なのでMAX10やCyclone10LPでもレベル変換なしでそのまま接続できます。

MCUが16MHz動作でPIOを直接操作しているため、速度としては数Mbps程度でそれほど高速ではありません。速度も純正のUSB-Blasterに比べて1/2~1/4といったところですが、NiosII dgbやSignalTapIIといったデバッグファンクションもきちんと動作します。

VID/PIDの問題があるので個人使用に留めておくべきですが、ローコストに出来るので趣味用途には十分でしょう。

2023-06-30 20:26

Tang-NANO届いた(追記あり) [FPGA]

SiPeedの激安FPGAボード、Tang-NANOがSeeedで販売になってたのでいくつかまとめて購入しました。

GOWINのツールは半年ぐらい前からインストールして触っていたのですが、現物含めたファーストインプレッションとしては‥‥

・GOWIN IDEツール

意外と使いやすい。SynplifyProで論理合成から配置配線までやるので、IDEはほぼガワだけの存在。そのうちVScodeのプラグインが出てきそう。

コンパイルはかなり高速だけどチューニング項目はあんまりない。タイミングを追い込んで使うようなヘビーな使い方を期待すると死ぬ。

ハードマクロを使うIPジェネレータや、組み込みロジアナなんかも一通り揃っている。

ただし、論理シミュレータがまったくないので、これだけで使おうとすると泥沼。QuartusPrime Liteと併用してModelSimを使うのが吉。

・Tang-NANOボード

使われているFPGAはGW1Nシリーズの一番小さいやつ。1152LUT+864FFで乗算器はなし。メモリマクロは18kbitのブロックRAMが4個。PLLが1個。コンフィグROMを内蔵しているので、MAX10の500~800LE相当な感じ。

オンボードにはJTAGダウンローダが載っているので、単体でGOWIN IDEのProgrammerからコンフィグレーションデータを書き込むことができる。

それ以外には64MbitのQSPI-SRAMが載ってる。所謂IoT-RAMと呼ばれているグループで、小ピン(6本)でそこそこ高速な大容量メモリを扱える。

ボード上には40ピンFPCも載っていて、4.3インチグラフィック液晶のデファクトスタンダード配置。専用の800x480 LCDの他、秋月で売ってる480x272 LCDも接続できる。

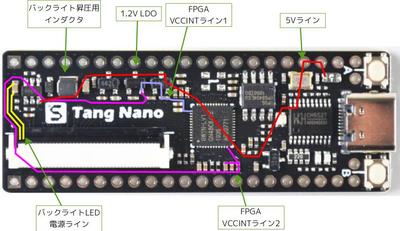

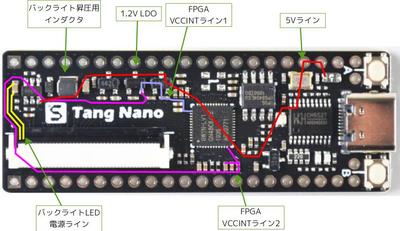

なかなかいい、と思いきやLCDバックライト昇圧回路が問題でした。

サンプルのコンフィグで指定のLCDを繋ぐとカラーバーは出る、しかしLCDを繋いでないときは点滅し続けるカラーLEDがLCDを繋いでいるときは途中で止まってしまう。しばらくほっとくとまた点滅を始める。

USBの電源供給の問題かと思ったので5V/2Aの充電器に繋いでみるも、やっぱり挙動は変わらない。

個体の問題かと思って別のボードを繋いで見ても同じ症状がでる。

こういう不可解な挙動をする場合、かなり高い確率でFPGAの電源系に問題を抱えています。

サージやドロップで部分的に内部ロジックの動作がおかしくなり、CRCチェックが回ってくると再コンフィグして復帰する、というパターン。

それでパターンを追いかけてみると、1.2Vの電源が1本、昇圧DC/DCのインダクタのそばを通り、ICの下をくぐってバックライトLEDラインと並走して、かなり大回りしてFPGAに接続されているのがわかりました。

また1.2V/3,3V LDOへの入力も昇圧用インダクタと十分なデカップリングがされていないので、1.2Vラインの電源品質はかなり悪いと考えられます。

基板のアートワークレベルの問題で、部品の載せ替え程度では解決しそうにないので、LCDを使う場合はオン

ボードのバックライト昇圧回路は切り離して、外部にバックライト電源を接続する必要がありそうです。

なんとか電源パターンのカット&ジャンパでどうにかできないか模索中。

で、とりあえずLチカ

追記。

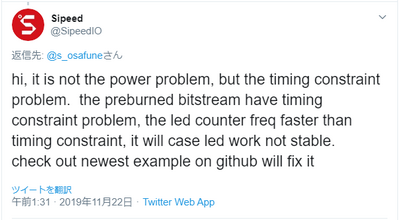

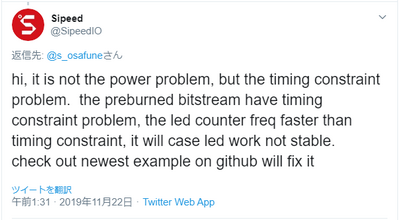

SiPeedからレスがあり、どうも出荷で書き込まれてるやつはタイミングmetに不具合があるようです。

さらに迅速にストレステストを実施してもらい、1.2Vの安定性を確認していただきました。

ただ、出力しかしないはずのLCDを接続するとおかしくなるのも、負荷のかかり方でシビアなタイミングの問題でてるとするならやはりボードなりデバイスなり電源まわりに弱い箇所があるのだろうとは思います。

上限を見極めたいので、こちらでももうちょっと調べています。

さらに追記。

1.2Vラインをジャンパして昇圧DC/DCをカットしたものと、無改造のものを比較測定しました。

接続したLCDは秋月のATM0430D5です。これに480x272のカラーパターンを表示させて電源ラインに重畳するノイズを見ました。

昇圧DC/DCの1.5MHzのノイズが定常で±60mV以上重畳していて、動作マージンはかなり厳しいと考えられます。タイミングぎりぎりのデザインはやらない方がいいですね。

GOWINのツールは半年ぐらい前からインストールして触っていたのですが、現物含めたファーストインプレッションとしては‥‥

・GOWIN IDEツール

意外と使いやすい。SynplifyProで論理合成から配置配線までやるので、IDEはほぼガワだけの存在。そのうちVScodeのプラグインが出てきそう。

コンパイルはかなり高速だけどチューニング項目はあんまりない。タイミングを追い込んで使うようなヘビーな使い方を期待すると死ぬ。

ハードマクロを使うIPジェネレータや、組み込みロジアナなんかも一通り揃っている。

ただし、論理シミュレータがまったくないので、これだけで使おうとすると泥沼。QuartusPrime Liteと併用してModelSimを使うのが吉。

・Tang-NANOボード

使われているFPGAはGW1Nシリーズの一番小さいやつ。1152LUT+864FFで乗算器はなし。メモリマクロは18kbitのブロックRAMが4個。PLLが1個。コンフィグROMを内蔵しているので、MAX10の500~800LE相当な感じ。

オンボードにはJTAGダウンローダが載っているので、単体でGOWIN IDEのProgrammerからコンフィグレーションデータを書き込むことができる。

それ以外には64MbitのQSPI-SRAMが載ってる。所謂IoT-RAMと呼ばれているグループで、小ピン(6本)でそこそこ高速な大容量メモリを扱える。

ボード上には40ピンFPCも載っていて、4.3インチグラフィック液晶のデファクトスタンダード配置。専用の800x480 LCDの他、秋月で売ってる480x272 LCDも接続できる。

なかなかいい、と思いきやLCDバックライト昇圧回路が問題でした。

サンプルのコンフィグで指定のLCDを繋ぐとカラーバーは出る、しかしLCDを繋いでないときは点滅し続けるカラーLEDがLCDを繋いでいるときは途中で止まってしまう。しばらくほっとくとまた点滅を始める。

USBの電源供給の問題かと思ったので5V/2Aの充電器に繋いでみるも、やっぱり挙動は変わらない。

個体の問題かと思って別のボードを繋いで見ても同じ症状がでる。

こういう不可解な挙動をする場合、かなり高い確率でFPGAの電源系に問題を抱えています。

サージやドロップで部分的に内部ロジックの動作がおかしくなり、CRCチェックが回ってくると再コンフィグして復帰する、というパターン。

それでパターンを追いかけてみると、1.2Vの電源が1本、昇圧DC/DCのインダクタのそばを通り、ICの下をくぐってバックライトLEDラインと並走して、かなり大回りしてFPGAに接続されているのがわかりました。

また1.2V/3,3V LDOへの入力も昇圧用インダクタと十分なデカップリングがされていないので、1.2Vラインの電源品質はかなり悪いと考えられます。

基板のアートワークレベルの問題で、部品の載せ替え程度では解決しそうにないので、LCDを使う場合はオン

ボードのバックライト昇圧回路は切り離して、外部にバックライト電源を接続する必要がありそうです。

なんとか電源パターンのカット&ジャンパでどうにかできないか模索中。

で、とりあえずLチカ

追記。

SiPeedからレスがあり、どうも出荷で書き込まれてるやつはタイミングmetに不具合があるようです。

さらに迅速にストレステストを実施してもらい、1.2Vの安定性を確認していただきました。

s_osafuneSiPeedでも実測してワーストコンディションについても1.2V系の安定性に問題無いとのことです。 https://t.co/6OnIPRWZPN11/22 23:10

ただ、出力しかしないはずのLCDを接続するとおかしくなるのも、負荷のかかり方でシビアなタイミングの問題でてるとするならやはりボードなりデバイスなり電源まわりに弱い箇所があるのだろうとは思います。

上限を見極めたいので、こちらでももうちょっと調べています。

さらに追記。

1.2Vラインをジャンパして昇圧DC/DCをカットしたものと、無改造のものを比較測定しました。

接続したLCDは秋月のATM0430D5です。これに480x272のカラーパターンを表示させて電源ラインに重畳するノイズを見ました。

s_osafune測定した。私感では「昇圧DC/DCの影響は無視して良いほど小さくなく、動くけど問題は潜在している」という結論。タイミングmetしてない部分や非同期部分にはクリティカルな影響があると思う。 https://t.co/1P56I7g8oY11/23 03:48

昇圧DC/DCの1.5MHzのノイズが定常で±60mV以上重畳していて、動作マージンはかなり厳しいと考えられます。タイミングぎりぎりのデザインはやらない方がいいですね。

2019-11-21 03:41

1/fゆらぎをHDLにしてみた [FPGA]

前回、間欠カオス法を整数化したので最低限度の18bit精度ででHDLしてみた(というか、正確にはHDL化を前提に必要ビット数を見積もっていたのだけども)。

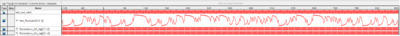

それで結論から先に言うと、どうやら18bit精度だと特定の値で繰り返しパターンに入ってしまうようだ。

これが実際にHDL実装したもののSignalTapで観測した様子。

綺麗に繰り返しパターンにはまってしまっててどうしたものかと考えていたところ、そもそもカオス系なんだから、フィードバックにちょっとだけノイズを混ぜてやれば安定系から崩れるのでは?と思い、2乗の値を加算する部分でLSBの1ビットだけランダムにひっくり返す処理を追加してみた。

と、こう書くとややこしい処理をいれたなと思われそうだけども、やってることはXorshit32の適当なビット(今回はMSBを使った)でフィードバックのLSBにXORをかけただけ。

結果はこう。

綺麗にカオス挙動に戻った。

ついでなので、乗算器を使ってないタイミングでランダム値の2乗計算を行って、rand値、rand^2値、1/f値を同時に取得できるように修正。

これで実装ロジック数は120LE+2DSPとかなりコンパクトになっている。

PWMでLEDをチカチカさせるとこんな感じ

それで結論から先に言うと、どうやら18bit精度だと特定の値で繰り返しパターンに入ってしまうようだ。

これが実際にHDL実装したもののSignalTapで観測した様子。

綺麗に繰り返しパターンにはまってしまっててどうしたものかと考えていたところ、そもそもカオス系なんだから、フィードバックにちょっとだけノイズを混ぜてやれば安定系から崩れるのでは?と思い、2乗の値を加算する部分でLSBの1ビットだけランダムにひっくり返す処理を追加してみた。

と、こう書くとややこしい処理をいれたなと思われそうだけども、やってることはXorshit32の適当なビット(今回はMSBを使った)でフィードバックのLSBにXORをかけただけ。

結果はこう。

綺麗にカオス挙動に戻った。

ついでなので、乗算器を使ってないタイミングでランダム値の2乗計算を行って、rand値、rand^2値、1/f値を同時に取得できるように修正。

これで実装ロジック数は120LE+2DSPとかなりコンパクトになっている。

PWMでLEDをチカチカさせるとこんな感じ

s_osafunePWMでLチカさせてみた。ノイズ発生器部分で120LE+2DSP https://t.co/exjEgt350O06/08 23:24

2019-06-08 23:53

VHDLいろいろ [FPGA]

今更感あるけども、VHDLで特定用途で便利な記述ネタを。

●コンポーネント宣言を省略する

を追加すると読み込んだエンティティのコンポーネント宣言を省略できる。VHDLの悪名の半分はこれで解消。

注意点はModelSimではコンパイル順で認識するので、ソースファイルの順番に依存してしまう。Quartusでは全てのファイルを読み込んでから評価するみたいなので同じプロジェクト内のソースであればどこでも参照できる。

●LPMやMegafunctionを直接インスタンスする

を追加しておくと、コンポーネント宣言を省略してLPMやMegafunctionのマクロをインスタンスできる。

乗算やFIFO、DDRIOなどハードマクロにインスタンスしたい場合に便利。

パラメータのマニュアルはIP Catalogで表示されるコンポーネント名でぐぐれはIntelのpdfがでてくるけど、そのままIP Catalogでソースを出力して該当部分をコピペした方が早い。

そんなわけで、ソース公開するときにライセンス云々でやかましい類の人間に噛みつかれたくないときに重宝。別にQuartusPrimeのツール生成ソースでライセンス上も何の問題も無いのだけれど。

●リダクション演算を使う

を追加すると以下のリダクション演算ファンクションが使えるようになる。

リダクション演算は引数のベクタの全ビットに対して論理演算を行うというもの。例えば and_reduce(data) とやると、dataの全ビットでand演算を行った結果が返される。つまり全ビットが'1'なら'1'が返る。

or_reduce(data)であれば全ビットが'0'の場合に'0'が返る。xor_reduce(data)では'1'のビットが奇数個の時に'1'が返る。

or_reduceは関係演算子でオーバーロードが行われるのでゼロ比較で代用できるけども、and_reduceの機能(任意長のビット幅で全ビットが'1'の判定)は少々面倒なので、パラメタラブルな記述をし始めると出番は多い。

●コンポーネント宣言を省略する

use work.all;

を追加すると読み込んだエンティティのコンポーネント宣言を省略できる。VHDLの悪名の半分はこれで解消。

注意点はModelSimではコンパイル順で認識するので、ソースファイルの順番に依存してしまう。Quartusでは全てのファイルを読み込んでから評価するみたいなので同じプロジェクト内のソースであればどこでも参照できる。

●LPMやMegafunctionを直接インスタンスする

library altera_mf;

use altera_mf.altera_mf_components.all;

library lpm;

use lpm.lpm_components.all;

を追加しておくと、コンポーネント宣言を省略してLPMやMegafunctionのマクロをインスタンスできる。

乗算やFIFO、DDRIOなどハードマクロにインスタンスしたい場合に便利。

パラメータのマニュアルはIP Catalogで表示されるコンポーネント名でぐぐれはIntelのpdfがでてくるけど、そのままIP Catalogでソースを出力して該当部分をコピペした方が早い。

そんなわけで、ソース公開するときにライセンス云々でやかましい類の人間に噛みつかれたくないときに重宝。別にQuartusPrimeのツール生成ソースでライセンス上も何の問題も無いのだけれど。

●リダクション演算を使う

use ieee.std_logic_misc.all;

を追加すると以下のリダクション演算ファンクションが使えるようになる。

and_reduce(std_logic_vector)

or_reduce(std_logic_vector)

xor_reduce(std_logic_vector)

nand_reduce(std_logic_vector)

nor_reduce(std_logic_vector)

xnor_reduce(std_logic_vector)

リダクション演算は引数のベクタの全ビットに対して論理演算を行うというもの。例えば and_reduce(data) とやると、dataの全ビットでand演算を行った結果が返される。つまり全ビットが'1'なら'1'が返る。

or_reduce(data)であれば全ビットが'0'の場合に'0'が返る。xor_reduce(data)では'1'のビットが奇数個の時に'1'が返る。

or_reduceは関係演算子でオーバーロードが行われるのでゼロ比較で代用できるけども、and_reduceの機能(任意長のビット幅で全ビットが'1'の判定)は少々面倒なので、パラメタラブルな記述をし始めると出番は多い。

2017-03-12 06:39

MAX10のコンフィグをシリアルUARTで書き換える [FPGA]

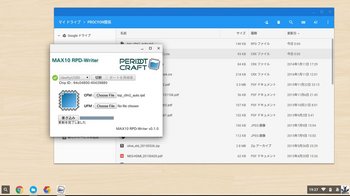

MAX10のデュアルコンフィグ機能を使って内蔵フラッシュを書き換えるツールをリリースしました。

→ MAX10 Serial Config Updater

Githubリポジトリ

→ max10_config_updater

・仕掛けの解説

MAX10のCFM0にブートローダとなるQsysモジュールを書き込んでおき、CONFIG_SEL='0' でまずこのイメージがブートされる。

ブートローダのQsysはPERIDOTのコンフィグレーション層(のエミュレーション)とAvalonMMブリッジを内蔵していて、これでQsysのシステムIDやチップユニークIDの読み出し、内蔵フラッシュの読み書き、デュアルブートコアのアクセスなどを行う。

ホストPCからはASモードに設定された(FPGAコンフィグ機能が使えない)PERIDOTの派生ボードとして見えているので、Canarium.jsのavmメソッドで内部アクセスができる。

MAX10の内蔵フラッシュペリフェラルはAvalonMMスレーブとしてメモリアドレスにマップされている。フラッシュ書き込みの待ち時間もAvalonMMのwaitrequestでハード的に行われるので、Canarium.jsからは単にメモリ領域の読み書きを行っているだけで済んでいる。

コンフィグレーションデータは32ビット単位でビット順を入れ替える必要があるものの、こういうのはChromeアプリ側でやってしまえるので、ハードウェア側で特別に対応する必要はない。

欠点としてはデュアルコンフィグをベースとするので、M9Kの初期値が使えない、CONFIG_SELピンがI/Oとして使えない&外部からH/Lを選択できないといけない、CFMをユーザー領域に使えない、などがある。

あと、一番最初のブートローダーを書き込むのにはUSB-Blasterが必要、というのは変わらないので、ここはなんとかしたい。ので、今はブートローダー書き込み済みのボードを販売できるよう準備を進めているところ。

チップ単品売りも考えてはいるけど、これは手間とか管理コストがかかるので、どこかしら代理店になってくれるとこがあれば。

Chromebookからも使えます。

→ MAX10 Serial Config Updater

Githubリポジトリ

→ max10_config_updater

・仕掛けの解説

MAX10のCFM0にブートローダとなるQsysモジュールを書き込んでおき、CONFIG_SEL='0' でまずこのイメージがブートされる。

ブートローダのQsysはPERIDOTのコンフィグレーション層(のエミュレーション)とAvalonMMブリッジを内蔵していて、これでQsysのシステムIDやチップユニークIDの読み出し、内蔵フラッシュの読み書き、デュアルブートコアのアクセスなどを行う。

ホストPCからはASモードに設定された(FPGAコンフィグ機能が使えない)PERIDOTの派生ボードとして見えているので、Canarium.jsのavmメソッドで内部アクセスができる。

MAX10の内蔵フラッシュペリフェラルはAvalonMMスレーブとしてメモリアドレスにマップされている。フラッシュ書き込みの待ち時間もAvalonMMのwaitrequestでハード的に行われるので、Canarium.jsからは単にメモリ領域の読み書きを行っているだけで済んでいる。

コンフィグレーションデータは32ビット単位でビット順を入れ替える必要があるものの、こういうのはChromeアプリ側でやってしまえるので、ハードウェア側で特別に対応する必要はない。

欠点としてはデュアルコンフィグをベースとするので、M9Kの初期値が使えない、CONFIG_SELピンがI/Oとして使えない&外部からH/Lを選択できないといけない、CFMをユーザー領域に使えない、などがある。

あと、一番最初のブートローダーを書き込むのにはUSB-Blasterが必要、というのは変わらないので、ここはなんとかしたい。ので、今はブートローダー書き込み済みのボードを販売できるよう準備を進めているところ。

チップ単品売りも考えてはいるけど、これは手間とか管理コストがかかるので、どこかしら代理店になってくれるとこがあれば。

Chromebookからも使えます。

2016-01-23 02:49

MAX10のデュアルコンフィグPOFを自動生成させたい [FPGA]

いまのとこQuartusPrimeは、MAX10のPOFはシングルイメージコンフィグではコンパイルフローで自動で生成されるものの、メモリ初期値付きの圧縮コンフィグとデュアルイメージコンフィグを使う場合はConvert Programming Filesで手作業で変換してやらないといけない。

USB-BlasterとQuartus Programmerでやる分にはSOFを直接流し込めるので、さほど手間ではないのだけれど、Chromeアプリとシリアル経由でコンフィグするPERIDOT Projectでは毎回RPDを生成せねばならず、なかなかに面倒くさい。

なので、MAX10のデュアルイメージコンフィグ用のファイル(POFと書き込み用RPD)を自動で生成するTclを作った。

→ auto_generate_dualboot_rpd.tcl

このtclファイルをプロジェクトフォルダの直下に置き、qsfファイルに以下の一行を追加する。(表示の都合で2行に折り返されてるけどそこは心眼で)

これでoutput_filesフォルダの下に自動でPOFとRPDが生成される。RPDは4ファイル生成され、各ファイルの内容は以下のとおり。

・<project名>_auto.rpd

内蔵フラッシュ全領域のイメージ

・<project名>_cfm0_auto.rpd

コンフィグレーション0領域のイメージ

・<project名>_cfm1_auto.rpd

コンフィグレーション1領域のイメージ

・<project名>_ufm_auto.rpd

ユーザーフラッシュ領域のイメージ

ただしこのTclで生成しているデータではcfm0とcfm1は同一でufmは利用しておらず、実際に使うのはcfm1のRPDだけ。

なお、このtclはMAX10のデュアルイメージコンフィグ専用なので、それ以外のコンフィグモードを使ってるプロジェクトに設定するとエラーで止まると思いまず。

USB-BlasterとQuartus Programmerでやる分にはSOFを直接流し込めるので、さほど手間ではないのだけれど、Chromeアプリとシリアル経由でコンフィグするPERIDOT Projectでは毎回RPDを生成せねばならず、なかなかに面倒くさい。

なので、MAX10のデュアルイメージコンフィグ用のファイル(POFと書き込み用RPD)を自動で生成するTclを作った。

→ auto_generate_dualboot_rpd.tcl

このtclファイルをプロジェクトフォルダの直下に置き、qsfファイルに以下の一行を追加する。(表示の都合で2行に折り返されてるけどそこは心眼で)

set_global_assignment -name POST_MODULE_SCRIPT_FILE "quartus_sh:auto_generate_dualboot_rpd.tcl"

これでoutput_filesフォルダの下に自動でPOFとRPDが生成される。RPDは4ファイル生成され、各ファイルの内容は以下のとおり。

・<project名>_auto.rpd

内蔵フラッシュ全領域のイメージ

・<project名>_cfm0_auto.rpd

コンフィグレーション0領域のイメージ

・<project名>_cfm1_auto.rpd

コンフィグレーション1領域のイメージ

・<project名>_ufm_auto.rpd

ユーザーフラッシュ領域のイメージ

ただしこのTclで生成しているデータではcfm0とcfm1は同一でufmは利用しておらず、実際に使うのはcfm1のRPDだけ。

なお、このtclはMAX10のデュアルイメージコンフィグ専用なので、それ以外のコンフィグモードを使ってるプロジェクトに設定するとエラーで止まると思いまず。

2016-01-20 05:02

MAX10の内蔵Flashを書き換える [FPGA]

MAX10のonchip flashコアはUFMセクタのみを使う場合と、CFMセクタも使う場合ではいろいろと作法が違うのでまとめました。

レジスタマッピングやインスタンスの諸々はMAX10フラッシュメモリユーザーガイドを参照のこと。

→ https://www.altera.co.jp/ja_JP/pdfs/literature/hb/max-10/ug_m10_ufm_j.pdf

■altera_onchip_flashコアの設定

基本的にQsysからAvalon-MMで利用する場合、インターフェースはPallarel、バースト長は2(10M04および08)または4(10M16以上)を選択する。

MAX10の内蔵Flashは5つのセクタからなり、アドレスの若い順にUFM1、UFM0、CFM2、CFM1、CFM0と並んでいる。

・UFM1,UFM0

全てのデバイス、全てのコンフィグレーションモードで利用可能。

UFMのみ初期値をConvert Programing Files→Options/Boot infoのUser Flash Memoryセクションで設定できる。

UFM souceでLoad memory fileを選択して、File pathにHEXまたはMIFを設定する。両方とも0x0000からの絶対アドレスで認識するため、アドレスオフセットは適宜調整しておく(特にHEX)。

・CFM2

FグレードおよびAグレードのデバイスでのみ利用可能。

コンフィグレーションモードがSingle Complessed imageまたはSingle Uncomplessed Imageの場合にはユーザー領域として利用することができる。

Dual Complessed imageの場合にはコンフィグイメージ1の領域として利用される。

・CFM1

FグレードおよびAグレードのデバイスでのみ利用可能。

コンフィグレーションモードがSingle Complessed imageの場合にはユーザー領域として利用することができる。

Dual Complessed imageの場合にはCFM2と共にコンフィグイメージ1の領域として利用される。

・CFM0

FグレードおよびAグレードのデバイスでのみ利用可能。

コンフィグレーションモードがDual Complessed imageの場合に利用可能。

コンフィグイメージ0の領域として利用され、ユーザー領域としての利用はできない。

altera_onchip_flashコアに設定するコンフィグレーションモードと、Quartus側のDevice and Pin Options→Configuration→Configuration schemeの設定は一致していなければならない。

またDual Complessed imageを設定した場合、CFM0にはコンフィグイメージ0、CFM1/2にはコンフィグイメージ1を格納するため、ユーザー用メモリとしては利用できない。

なお、コンフィグレーションモードにDual Complessed imageを選択した場合、そのデザインには必ずaltera_dual_bootコアを含めなければならない。

■セクタの消去とプログラミング

セクタの消去はcsrスレーブへのアクセスで行う。

セクタのプロテクトビットと、セクタイレース、ページイレースのビットが同じコントロールレジスタに存在しているため、プロテクトビット解除→イレース指示の2回のレジスタ操作が必要。

イレース発行後はステータスレジスタで消去の完了を確認する。

以下はCFM2セクタのイレースを行うコード例。

セクタのプログラミングは該当のメモリアドレスへ書き込むことで行う。

書き込み先のセクタは予めコントロールセクタの保護ビットを解除しておく必要がある。イレースと異なり、プログラミングの場合は複数セクタの保護ビットをクリアしておくことが可能。

セクタへの書き込みはAvalon-MMマスタから行う場合は書き込み完了までwaitrequestが発行されるため、ステータスレジスタで待ち時間を取る必要はない。ただし、書き込み時にはシングルアクセスで行う必要があり、NiosII /fコア等でバーストアクセスを持つマスタから書き込む場合には正しくシングルアクセスが行われるよう注意すること。

以下はCFM2、CFM1のプログラミングを行うコード例。

CFMにコンフィグレーションデータを書き込む場合、Avalon-MMから見えるビット順とコンフィグレーションストリームとして読み出されるビット順が32bit単位で逆になっているので、RPDファイルを書き込む際にビット順を逆にする必要がある。

ビット逆順の操作はコンフィグレーションデータのみに行う。UFMとして使う場合は読み書き共にAvalon-MMのビット順で行われるため不要。

■Dual Complessed imageデータの作成

Dual Complessed image用のコンフィグデータは自動では作られないので、コンパイル後にConvert Programming Filesで専用のPOFを作成する必要がある。

Programming file typeで.pofを選択した状態で、Mode:プルダウンでInternal Configurationを選択する。

UFMに初期値を設定する場合はOptionsボタンのUser Flash MemoryセクションでHEX/MIFを設定する。

Input files to convertタブにSOF Dataを2つ追加する。

ここで追加できるのは両方ともコンフィグレーションスキームでDual Complessed imageを設定したsofのみ。それ以外のsofは設定できない。また、sofを1つだけ設定することもできない。

片方のイメージだけ利用する場合、両方に同じsofを設定してpofを生成する必要がある。

Quartus Programmer以外の手法でCFMを書き換える場合、Create config data RPDにチェックを入れておく。

RPDファイルを生成した場合、全領域用のfoo_auto.rpd、CFM0(イメージ0)用のfoo_cfm0_auto.rpd、CFM1/2(イメージ1)用のfoo_cfm1_auto.rpd、UFM0/1用のfoo_ufm_auto.rpdの4つのファイルが作られる。

Dual Complessed imageを設定する場合にはもう一つ、CONFIG_SELピンの扱いがある。Device and Pin OptionsのGeneralでEnable CONFIG_SEL pinにチェックを外すと、必ずイメージ0のコンフィグで起動する。この場合イメージ1へはイメージ0のaltera_dual_bootコアでリコンフィグレーションすることになるため、CONFIG_SELピンを使用しない場合はdual_bootコアを操作できるAvalon-MMマスタが存在しなければならない。これがないとイメージ0のデータが破損しない限りイメージ1へのスイッチが行われない。

イメージ1のコンフィグを直接ブートする場合は、イメージ0、1両方のデバイス設定でEnable CONFIG_SEL pinにチェックを入れておかなければならない。

■MAX10のコンフィグレーションについて

MAX10の内蔵Flashはaltera_onchip_flashコアを使って書き換える事ができるが、MAX10のコンフィグレーションスキームを書き換えることはできない。例えばDual complessed imageのPOFを書き込んだ後にCFMにSingle Complessed imageを書き込んでもブートできない。

これはMAX10のコンフィグレーションスキームを格納する領域(ICB)はPOFでしか書き込む事ができないため。

altera_onchip_flashコアで行えるのは、あくまで同一コンフィグレーションスキームのデータ差し替えに限定されることに注意しなければならない。

レジスタマッピングやインスタンスの諸々はMAX10フラッシュメモリユーザーガイドを参照のこと。

→ https://www.altera.co.jp/ja_JP/pdfs/literature/hb/max-10/ug_m10_ufm_j.pdf

■altera_onchip_flashコアの設定

基本的にQsysからAvalon-MMで利用する場合、インターフェースはPallarel、バースト長は2(10M04および08)または4(10M16以上)を選択する。

MAX10の内蔵Flashは5つのセクタからなり、アドレスの若い順にUFM1、UFM0、CFM2、CFM1、CFM0と並んでいる。

・UFM1,UFM0

全てのデバイス、全てのコンフィグレーションモードで利用可能。

UFMのみ初期値をConvert Programing Files→Options/Boot infoのUser Flash Memoryセクションで設定できる。

UFM souceでLoad memory fileを選択して、File pathにHEXまたはMIFを設定する。両方とも0x0000からの絶対アドレスで認識するため、アドレスオフセットは適宜調整しておく(特にHEX)。

・CFM2

FグレードおよびAグレードのデバイスでのみ利用可能。

コンフィグレーションモードがSingle Complessed imageまたはSingle Uncomplessed Imageの場合にはユーザー領域として利用することができる。

Dual Complessed imageの場合にはコンフィグイメージ1の領域として利用される。

・CFM1

FグレードおよびAグレードのデバイスでのみ利用可能。

コンフィグレーションモードがSingle Complessed imageの場合にはユーザー領域として利用することができる。

Dual Complessed imageの場合にはCFM2と共にコンフィグイメージ1の領域として利用される。

・CFM0

FグレードおよびAグレードのデバイスでのみ利用可能。

コンフィグレーションモードがDual Complessed imageの場合に利用可能。

コンフィグイメージ0の領域として利用され、ユーザー領域としての利用はできない。

altera_onchip_flashコアに設定するコンフィグレーションモードと、Quartus側のDevice and Pin Options→Configuration→Configuration schemeの設定は一致していなければならない。

またDual Complessed imageを設定した場合、CFM0にはコンフィグイメージ0、CFM1/2にはコンフィグイメージ1を格納するため、ユーザー用メモリとしては利用できない。

なお、コンフィグレーションモードにDual Complessed imageを選択した場合、そのデザインには必ずaltera_dual_bootコアを含めなければならない。

■セクタの消去とプログラミング

セクタの消去はcsrスレーブへのアクセスで行う。

セクタのプロテクトビットと、セクタイレース、ページイレースのビットが同じコントロールレジスタに存在しているため、プロテクトビット解除→イレース指示の2回のレジスタ操作が必要。

イレース発行後はステータスレジスタで消去の完了を確認する。

以下はCFM2セクタのイレースを行うコード例。

IOWR(FLASH_CSR_BASE, 1, 0xfdffffff); // CFM2のプロテクトを解除

IOWR(FLASH_CSR_BASE, 1, 0xfdbffff); // CFM2のセクタイレースを発行

while((IORD(FLASH_CSR_BASE, 0) & 0x3) != 0x0) {} // セクタ消去終了を待つ

if ( (IORD(FLASH_CSR_BASE, 0) & 0x10) ) { // 消去の可否

printf("Erase CFM2 success.\n");

} else {

printf("Erase CFM2 failed.\n");

}

セクタのプログラミングは該当のメモリアドレスへ書き込むことで行う。

書き込み先のセクタは予めコントロールセクタの保護ビットを解除しておく必要がある。イレースと異なり、プログラミングの場合は複数セクタの保護ビットをクリアしておくことが可能。

セクタへの書き込みはAvalon-MMマスタから行う場合は書き込み完了までwaitrequestが発行されるため、ステータスレジスタで待ち時間を取る必要はない。ただし、書き込み時にはシングルアクセスで行う必要があり、NiosII /fコア等でバーストアクセスを持つマスタから書き込む場合には正しくシングルアクセスが行われるよう注意すること。

以下はCFM2、CFM1のプログラミングを行うコード例。

IOWR(FLASH_CSR_BASE, 1, 0xf9ffffff); // CFM2,CFM1のプロテクトを解除

for(i=CFM2_START_ADDR ; i<=CFM1_END_ADDR ; i+=4) {

confdata = bit_reverse_u32(*rpddata++); // 32bit単位でビットを逆順にする

IOWR_DIRECT32(FLASH_DATA_BASE, i, confdata); // 書き込み実行

if ( !(IORD(FLASH_CSR_BASE, 0) & 0x8) ) { // 書き込みの可否

printf("Write to 0x%x failed.\n", i);

break;

}

}

IOWR(FLASH_CSR_BASE, 1, 0xffffffff); // 全セクタプロテクト

CFMにコンフィグレーションデータを書き込む場合、Avalon-MMから見えるビット順とコンフィグレーションストリームとして読み出されるビット順が32bit単位で逆になっているので、RPDファイルを書き込む際にビット順を逆にする必要がある。

ビット逆順の操作はコンフィグレーションデータのみに行う。UFMとして使う場合は読み書き共にAvalon-MMのビット順で行われるため不要。

■Dual Complessed imageデータの作成

Dual Complessed image用のコンフィグデータは自動では作られないので、コンパイル後にConvert Programming Filesで専用のPOFを作成する必要がある。

Programming file typeで.pofを選択した状態で、Mode:プルダウンでInternal Configurationを選択する。

UFMに初期値を設定する場合はOptionsボタンのUser Flash MemoryセクションでHEX/MIFを設定する。

Input files to convertタブにSOF Dataを2つ追加する。

ここで追加できるのは両方ともコンフィグレーションスキームでDual Complessed imageを設定したsofのみ。それ以外のsofは設定できない。また、sofを1つだけ設定することもできない。

片方のイメージだけ利用する場合、両方に同じsofを設定してpofを生成する必要がある。

Quartus Programmer以外の手法でCFMを書き換える場合、Create config data RPDにチェックを入れておく。

RPDファイルを生成した場合、全領域用のfoo_auto.rpd、CFM0(イメージ0)用のfoo_cfm0_auto.rpd、CFM1/2(イメージ1)用のfoo_cfm1_auto.rpd、UFM0/1用のfoo_ufm_auto.rpdの4つのファイルが作られる。

Dual Complessed imageを設定する場合にはもう一つ、CONFIG_SELピンの扱いがある。Device and Pin OptionsのGeneralでEnable CONFIG_SEL pinにチェックを外すと、必ずイメージ0のコンフィグで起動する。この場合イメージ1へはイメージ0のaltera_dual_bootコアでリコンフィグレーションすることになるため、CONFIG_SELピンを使用しない場合はdual_bootコアを操作できるAvalon-MMマスタが存在しなければならない。これがないとイメージ0のデータが破損しない限りイメージ1へのスイッチが行われない。

イメージ1のコンフィグを直接ブートする場合は、イメージ0、1両方のデバイス設定でEnable CONFIG_SEL pinにチェックを入れておかなければならない。

■MAX10のコンフィグレーションについて

MAX10の内蔵Flashはaltera_onchip_flashコアを使って書き換える事ができるが、MAX10のコンフィグレーションスキームを書き換えることはできない。例えばDual complessed imageのPOFを書き込んだ後にCFMにSingle Complessed imageを書き込んでもブートできない。

これはMAX10のコンフィグレーションスキームを格納する領域(ICB)はPOFでしか書き込む事ができないため。

altera_onchip_flashコアで行えるのは、あくまで同一コンフィグレーションスキームのデータ差し替えに限定されることに注意しなければならない。

2016-01-09 09:14

オンラインショップ開設 [FPGA]

PERIDOT CRAFTの常設オンラインショップが開設しました。

→ PERIDOT CRAFTオンラインショップ

ニコ技イベントやMaker Faireなどで販売した在庫や、処分品などのスポット品を取り扱っていきます。

またPERIDOT CRAFTのイベント出展情報などもコチラで発信しますので、週一チェック推奨です。ヨロシク!

→ PERIDOT CRAFTオンラインショップ

ニコ技イベントやMaker Faireなどで販売した在庫や、処分品などのスポット品を取り扱っていきます。

またPERIDOT CRAFTのイベント出展情報などもコチラで発信しますので、週一チェック推奨です。ヨロシク!

2015-10-21 04:06

FPGAマガジン過去記事フォロー [FPGA]

FPGAマガジン1号~3号のNiosII記事のサンプルバイナリをこちらでも公開します。

No.1 cq_viola_v1.zip(1.3Mバイト)

No.2 cq_viola_v2.zip(1.1Mバイト)

No.3 cq_viola_v3.zip(1.2Mバイト)

※2021/11/04 リンク先が消失していたので修正しました

No.1 cq_viola_v1.zip(1.3Mバイト)

No.2 cq_viola_v2.zip(1.1Mバイト)

No.3 cq_viola_v3.zip(1.2Mバイト)

※2021/11/04 リンク先が消失していたので修正しました

高速ビデオ・インターフェース×FPGA (FPGAマガジン No.1): ディジタル表示回路を作ってモニタを直ドライブ

- 作者:

- 出版社/メーカー: CQ出版

- 発売日: 2013/09/04

- メディア: 単行本

USB 3.0 × FPGA (FPGAマガジン No.2)

- 作者:

- 出版社/メーカー: CQ出版

- 発売日: 2013/11/27

- メディア: 単行本

高速Ethernet × FPGA (FPGAマガジン No.3)

- 作者:

- 出版社/メーカー: CQ出版

- 発売日: 2014/04/12

- メディア: 単行本

2015-04-30 13:31

どこでも入店チャイム [FPGA]

先に発売されたFPGAマガジン9号に記事かきました。

本文中では大人の事情により明言されていませんが、ナショナル電工のEC522をFPGAで再現してます。サブカル的にわかりやすく言えばファミマチャイムです。

Githubリポジトリはこちら

→github.com/osafune/CQEXT_melodychime

DE0じゃないけど動作してるところ

ところでこのメロディサイン、オリジナルはMN6221DというオルゴールICで作られていて、基本発振やエンベロープはアナログ回路で作られてます。

なので外部回路のつくりかたで結構音色が変わってくるわけですが、今回はニコ技の尻Pこと野尻抱介先生が、過去にニコニコ動画でファミマチャイムが盛り上がった時期に公開された実機からの録音データをリファレンスとして使わせてもらいました。

→2009-09-09 ファミマ入店音(野尻blog)

ここのWAV波形から基本周波数とエンベロープの時定数を取っているので、アナログ部分の癖は野尻先生宅のEC522のクローンになってます。

野尻先生といえば「南極点のピアピア動画」にてコンビニエンスストアを舞台にしたSFを書かれています。ちなみに作中のコンビニ(ハミングマート)のチャイムにはアルテラ製FPGAが使われている設定で、その点からいえばこれはファミマチャイムというよりも、作中の「ハミマチャイム」であると言えましょう。

本文中では大人の事情により明言されていませんが、ナショナル電工のEC522をFPGAで再現してます。サブカル的にわかりやすく言えばファミマチャイムです。

Githubリポジトリはこちら

→github.com/osafune/CQEXT_melodychime

DE0じゃないけど動作してるところ

ところでこのメロディサイン、オリジナルはMN6221DというオルゴールICで作られていて、基本発振やエンベロープはアナログ回路で作られてます。

なので外部回路のつくりかたで結構音色が変わってくるわけですが、今回はニコ技の尻Pこと野尻抱介先生が、過去にニコニコ動画でファミマチャイムが盛り上がった時期に公開された実機からの録音データをリファレンスとして使わせてもらいました。

→2009-09-09 ファミマ入店音(野尻blog)

ここのWAV波形から基本周波数とエンベロープの時定数を取っているので、アナログ部分の癖は野尻先生宅のEC522のクローンになってます。

野尻先生といえば「南極点のピアピア動画」にてコンビニエンスストアを舞台にしたSFを書かれています。ちなみに作中のコンビニ(ハミングマート)のチャイムにはアルテラ製FPGAが使われている設定で、その点からいえばこれはファミマチャイムというよりも、作中の「ハミマチャイム」であると言えましょう。

2015-04-25 23:23