MAX10のUFMでNiosIIをブートする方法 [FPGA]

1.前準備

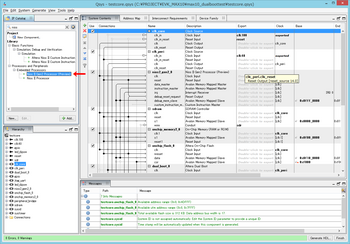

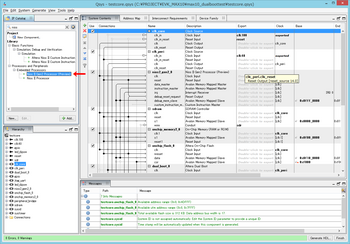

NiosII Gen2とUFMとメモリをQsysでインスタンスする。

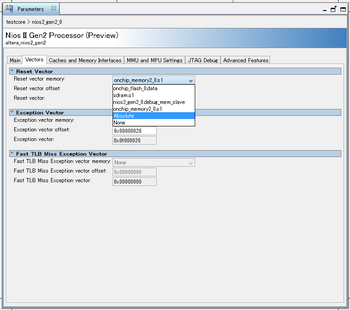

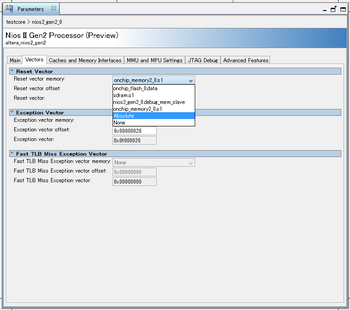

NiosIIのリセットベクタをUFMに割り当てる。Exceptionベクタは適宜。

IDEでプロジェクトを作成。

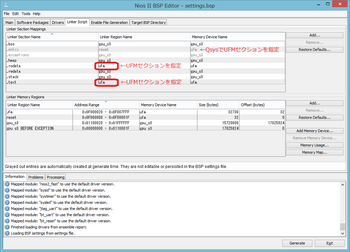

2.BSPの設定

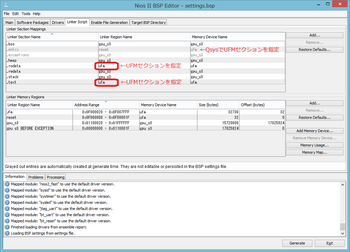

LinkerタブでrodataセクションとtextセクションをUFMに割り当てる。

bss、heap、rwdata、stackのセクションはメモリに割り当てる。

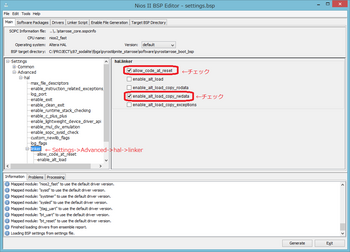

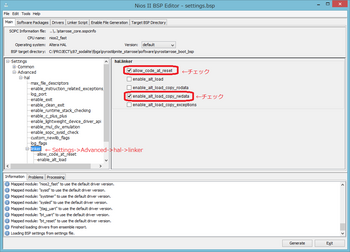

Settings→Advanced→hal→linkerでallow_code_at_resetとenable_alt_load_copy_rwdataにチェックを入れる。Exceptionベクタをメモリに置いている場合はさらにenable_alt_load_copy_exceptionにもチェックを入れておく。

GenerateでBSPを生成してプロジェクトをビルドする。

3.elfファイルをHEXファイルに変換

IDEでビルドしたelfファイルをメモリ初期値ファイルに変換する。

NiosII Shellを立ち上げてIDEプロジェクトのフォルダへ移動後、次のようにする。

UFMは32kバイトのうち、前半16kバイトと後半16kバイトに分かれているが、POFにパッキングするときはまとめて32kバイトとして扱われる。

正しくBSPが設定されている場合、UFMのリセットベクタ(先頭32バイト)に実効コードへのジャンプ命令が追加されている(HEXファイルの2行目のデータフィールドが0で埋まってなければOK)

ちなみにhexファイル名は自由に付けてOK。

注意するのはその後、UFMの要素はバイト列なので --width=8 の指定を忘れないこと。

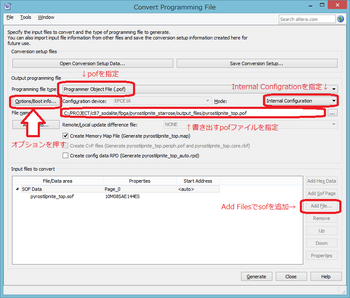

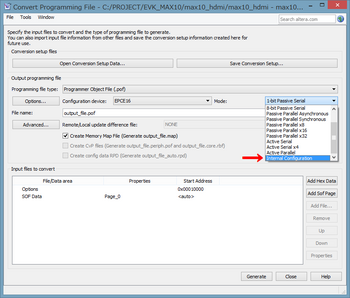

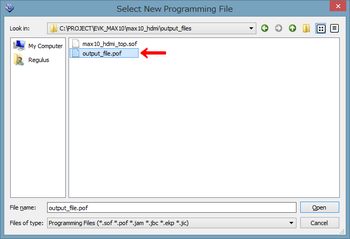

4.POFファイルを生成

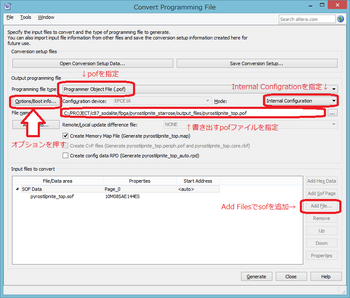

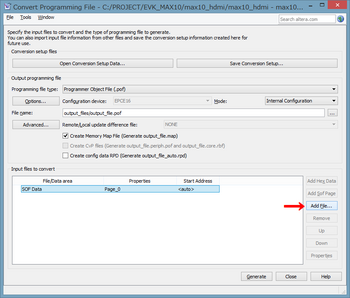

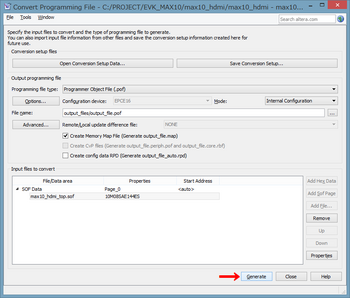

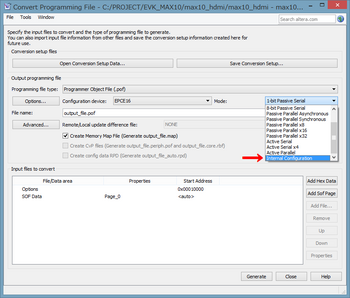

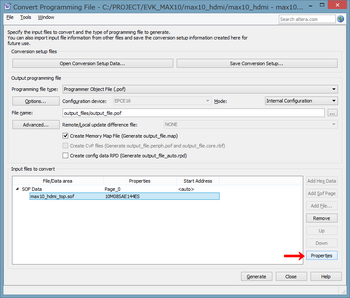

QuartusIIに戻って、File→Convert Programming Files...を選択。

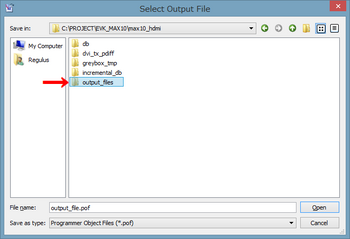

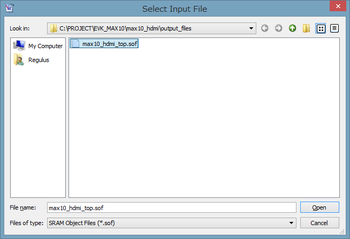

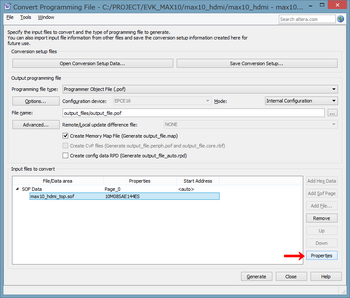

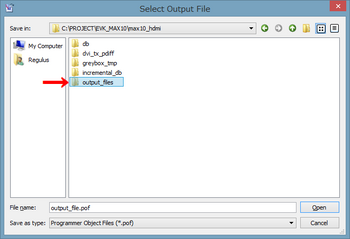

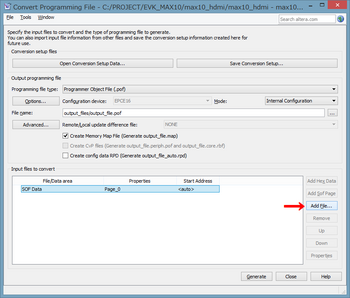

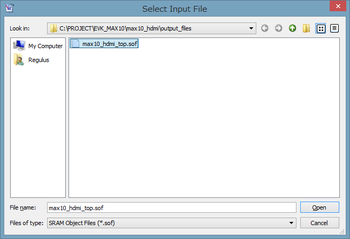

ファイルタイプはPOFを指定。ModeにはInernal Configrationを指定。出力ファイル名を指定して、Add Filesでsofファイルを追加する。

なお、最初にConfigration deviceがEPCEになってないと、ModeのプルダウンにInternal Configrationが出てこないので注意。

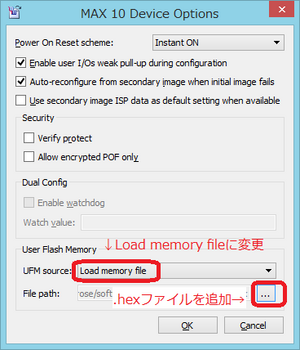

全部設定できたら、Options/Boot info...をクリックして次へ

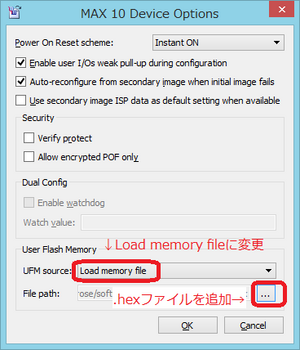

UFM sourceをLoad memory fileに変更して、File pathに先ほど生成したhexファイルを指定する。

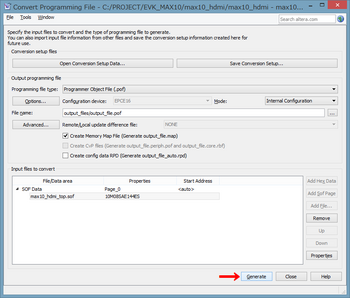

全部設定できたらGenerateボタンでPOFを生成する。

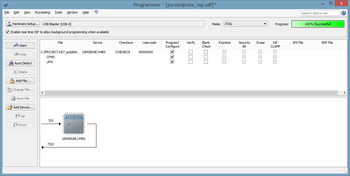

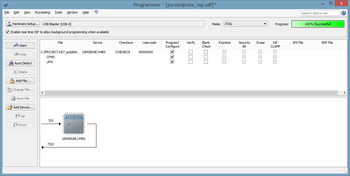

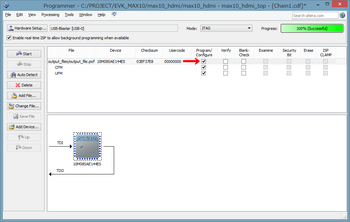

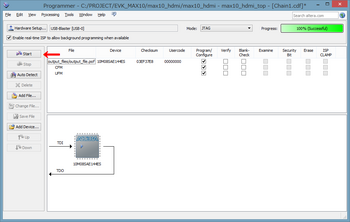

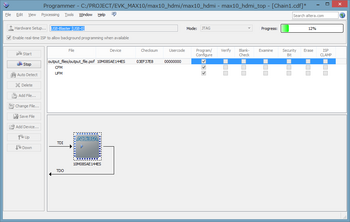

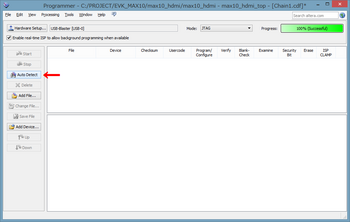

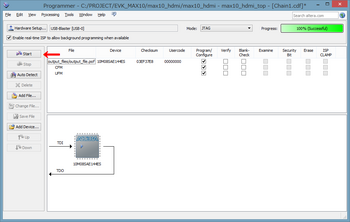

5.書き込み

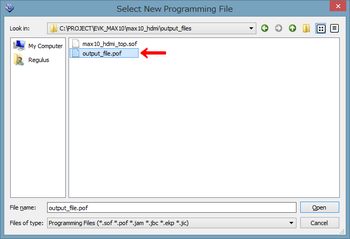

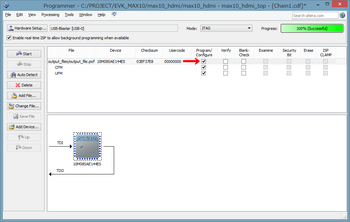

ProgrammerでPOFファイルをMAX10に書き込む。

UFMのみにチェックをつければ、UFM部分だけを書き換えることができる。

デバイスをリブートすればUFMのコードでNiosIIが実行される。

NiosII Gen2とUFMとメモリをQsysでインスタンスする。

NiosIIのリセットベクタをUFMに割り当てる。Exceptionベクタは適宜。

IDEでプロジェクトを作成。

2.BSPの設定

LinkerタブでrodataセクションとtextセクションをUFMに割り当てる。

bss、heap、rwdata、stackのセクションはメモリに割り当てる。

Settings→Advanced→hal→linkerでallow_code_at_resetとenable_alt_load_copy_rwdataにチェックを入れる。Exceptionベクタをメモリに置いている場合はさらにenable_alt_load_copy_exceptionにもチェックを入れておく。

GenerateでBSPを生成してプロジェクトをビルドする。

3.elfファイルをHEXファイルに変換

IDEでビルドしたelfファイルをメモリ初期値ファイルに変換する。

NiosII Shellを立ち上げてIDEプロジェクトのフォルダへ移動後、次のようにする。

$ elf2hex --base=<UFM先頭アドレス> --end=<UFM終了アドレス> --input=<elfファイル> --output=boot.hex --width=8

UFMは32kバイトのうち、前半16kバイトと後半16kバイトに分かれているが、POFにパッキングするときはまとめて32kバイトとして扱われる。

正しくBSPが設定されている場合、UFMのリセットベクタ(先頭32バイト)に実効コードへのジャンプ命令が追加されている(HEXファイルの2行目のデータフィールドが0で埋まってなければOK)

ちなみにhexファイル名は自由に付けてOK。

注意するのはその後、UFMの要素はバイト列なので --width=8 の指定を忘れないこと。

4.POFファイルを生成

QuartusIIに戻って、File→Convert Programming Files...を選択。

ファイルタイプはPOFを指定。ModeにはInernal Configrationを指定。出力ファイル名を指定して、Add Filesでsofファイルを追加する。

なお、最初にConfigration deviceがEPCEになってないと、ModeのプルダウンにInternal Configrationが出てこないので注意。

全部設定できたら、Options/Boot info...をクリックして次へ

UFM sourceをLoad memory fileに変更して、File pathに先ほど生成したhexファイルを指定する。

全部設定できたらGenerateボタンでPOFを生成する。

5.書き込み

ProgrammerでPOFファイルをMAX10に書き込む。

UFMのみにチェックをつければ、UFM部分だけを書き換えることができる。

デバイスをリブートすればUFMのコードでNiosIIが実行される。

2015-04-04 05:48

CLIでQuartusIIを使ってみる [FPGA]

通常、Linux版のQuartusIIをインストールするにはX環境が必要なんだけど、サーバーみたいなCLIのみの環境でも使えたのでまとめてみた。

環境はさくらVPSのCentOS 6.3/64bit

1.ダウンロード

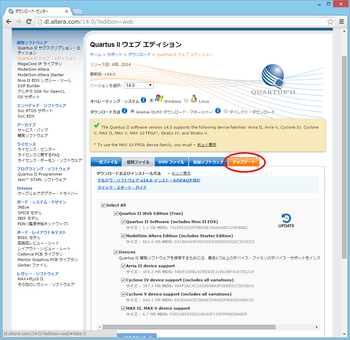

まずアルテラのダウンロードページからQuartusII WebEditionのLinux版をダウンロードする。

デバイスライブラリはとりあえずCycloneIVだけ。

2.VPSに転送

SSHでログインして、SCPでcyclone-14.1.0.186.qrzとQuartusSetupWeb-14.1.0.186-linux.runをコピー。

.qrzは.runと同じディレクトリに置いておく。

3.インストール

実行パーミッションを追加してインストーラをテキストモードで起動

4.環境変数を追加

.bashrcにパスを追加してシェルを再起動

これで

を実行してみてヘルプが出てくれば環境構築はOK

5.プロジェクトファイル

今回はサーバー側でコンパイルを走らせるのが目的なので、プロジェクトファイルは別に用意した。

WindowsやLinuxクライアント環境のQuartusIIでプロジェクトを作成し、qsfファイルとソースファイルをftpやscpでVPSの任意フォルダ(ここではqpf_workとする)に転送後

でコンパイル→TimeQuest解析まで実行される。

コマンドラインスクリプトの詳細はQuartusIIハンドブック Vol.2 の Command Line Scripting(英語版PDF)を参照。

Linux環境メインの人はあんまり関係なさげだけども、Windows環境からデータを持っていく場合、日本語コードが混ざってるソースはUTF-8Nにしておくのが無難。

また、.shや.tclなどのスクリプトファイルについては改行コードもCR+LFからLFのみにしておかないと、CRが悪さをすることがあるので注意。

環境はさくらVPSのCentOS 6.3/64bit

1.ダウンロード

まずアルテラのダウンロードページからQuartusII WebEditionのLinux版をダウンロードする。

デバイスライブラリはとりあえずCycloneIVだけ。

2.VPSに転送

SSHでログインして、SCPでcyclone-14.1.0.186.qrzとQuartusSetupWeb-14.1.0.186-linux.runをコピー。

.qrzは.runと同じディレクトリに置いておく。

3.インストール

実行パーミッションを追加してインストーラをテキストモードで起動

$ chmod +x QuartusSetupWeb-14.1.0.186-linux.run

$ ./QuartusSetupWeb-14.1.0.186-linux.run --mode text

4.環境変数を追加

.bashrcにパスを追加してシェルを再起動

PATH="$PATH":<ホームパス>/altera/14.1/quartus/bin

これで

$ quartus_sh --help

を実行してみてヘルプが出てくれば環境構築はOK

5.プロジェクトファイル

今回はサーバー側でコンパイルを走らせるのが目的なので、プロジェクトファイルは別に用意した。

WindowsやLinuxクライアント環境のQuartusIIでプロジェクトを作成し、qsfファイルとソースファイルをftpやscpでVPSの任意フォルダ(ここではqpf_workとする)に転送後

$ cd qpf_work

$ quartus_sh --flow compile <プロジェクト名>

でコンパイル→TimeQuest解析まで実行される。

コマンドラインスクリプトの詳細はQuartusIIハンドブック Vol.2 の Command Line Scripting(英語版PDF)を参照。

Linux環境メインの人はあんまり関係なさげだけども、Windows環境からデータを持っていく場合、日本語コードが混ざってるソースはUTF-8Nにしておくのが無難。

また、.shや.tclなどのスクリプトファイルについては改行コードもCR+LFからLFのみにしておかないと、CRが悪さをすることがあるので注意。

2015-04-01 19:25

MAX10デバイスを使う場合の注意まとめ(その1) [FPGA]

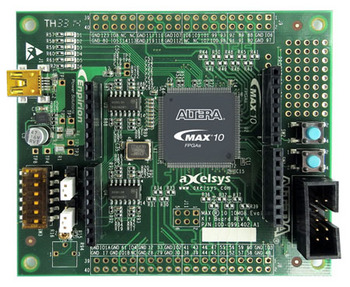

さて、先月からMAX10デバイスを一通り使ってみて、途中基板を速攻で起こす羽目になったりしてプチ修羅場な状況だったのだけども、なんとか収束してきたのでMAX10を使うにあたってのまとめをしてみよう。

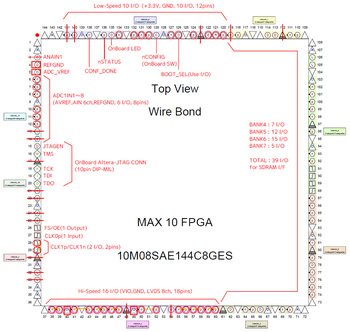

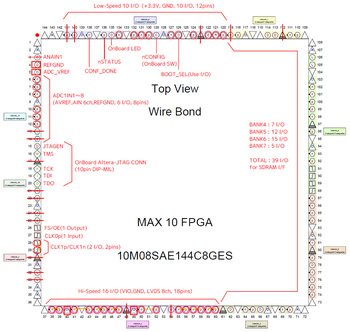

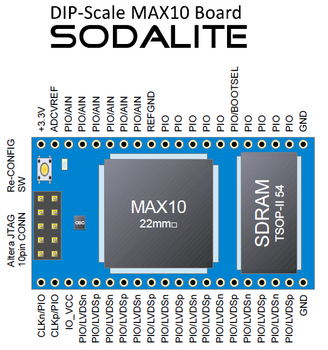

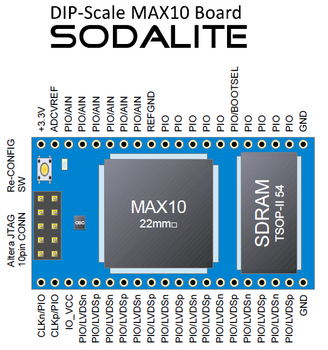

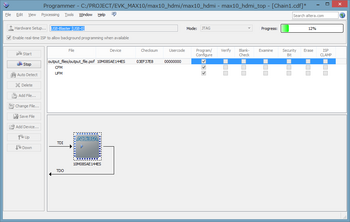

MAX10はラインナップ上いくつかのバリエーションがあるものの、ここでは全部網羅することはできないので、MAX10 evalボードおよびSODALITE基板で採用の10M08SAE144C8GESに限って話をすすめることにします。それ以外のデバイスについては適宜データシートを参照のこと。

→ オンライン資料:MAX 10 FPGA

1.コンパイル編

まずQuartusIIでのコンパイルから。

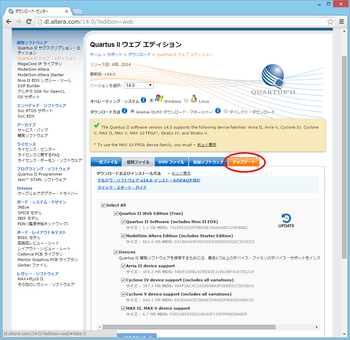

MAX10はまだQuartusIIでは正式に対応している状態ではなく、14.0のアップデートパッチ(Update2)による暫定対応となっています(正式対応は14.1で、これは来週のALTERAサーバーメンテ開けにリリースされるものと思われる)。

→ 参照:MAX10ボードがもうすぐ到着

QuartusII 14.0をインストール後、Update2パッチをインストールすることでMAX10デバイスが選択できるようになります。また14.0 Update2ではラインナップのうち、10M02/10M04/10M08と10M40および50がライブラリとして用意されており、まだ全ラインナップが揃っていません。

次にコンパイルに関しても、MAX10では既存のFPGAデバイスとはくせの違う部分があります。

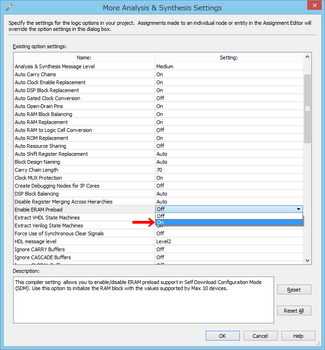

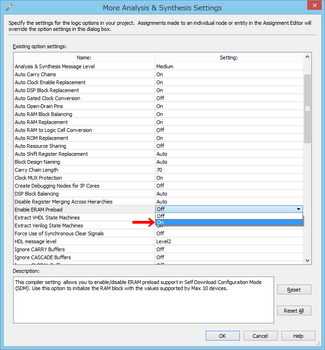

大きな差の一つが、メモリマクロの初期値についての問題で、MAX10デバイスで初期値付きのメモリを使う場合は Settings→Analysys&Synthesis→More Settings で追加設定を開き、その中のEnable ERAM PreloadをOff→Onにします。

→ 参照:MAX 10 エンベデッド・メモリ・ユーザーガイド(4-6 注釈)

2.書き込み編

続いてデバイスへのダウンロード。

14.0 Update2ではSOFまでしか生成されず、POFは手動で生成してやる必要があります。

→ 参照:MAX10ボード使ってみた

ここで注意しないといけないのは、MAX10では(少なくとも現段階では)何もコンフィグレーションされてない状態ではPOFの書き込みが出来ない点です。これはかなりハマりました‥‥。

なので、予め何らかのSOFをダウンロードしてMAX10デバイス内部をコンフィグレーションさせておく必要があります。

MAX10 evalボードでは最初にテストコンフィグが入っていますが、デバイスイレースをすると未コンフィグ状態になるので注意が必要です。

またもう一つ、MAX10デバイスのES品では出荷時にリコンフィグレーション・タイムアウト機能が有効になっていて、何も書き込まずにSOFだけダウンロードしていると勝手にリコンフィグします。傍目にはブラウンアウトリセットがかかったように見えるのでタチが悪い‥‥。

リコンフィグレーション・タイムアウト機能の解除の仕方はErrata Sheet and Guidelines for MAX 10 ES Devices (英語版・PDF)の最後に記載がありますが

イレースしただけではタイムアウト機能はそのままなので、いったん電源を入れ直してデバイス内部を初期化し直す必要があります。

このリコンフィグレーション・タイムアウト機能のやっかいなところは、POFの書き込みにかかる時間よりもタイムアウト時間の方が短いため、最初にこの機能をOFFにしとかないとPOFの書き込みが途中で失敗する(勝手にリコンフィグする)ことです。これまただいぶハマった‥‥。

ところで、うちの環境ではUSB-Blaster Rev.Bの接続で、MAX10 evalボードでもSODALITEボードでもJTAGのリンクが頻繁に切れるという問題が発生してます。

レベル変換を省いてMAX3000A直結のクローンBlasterでは問題が出てないあたり、どうもUSB-Blaster Rev.Bの電気仕様とMAX10のJTAGピンの電気仕様の相性がよろしくないのかもしれません。

単にうちのUSB-Blasterが死にかけなだけかもしれませんが、まあそういう事例も出てますということで。

3.NiosII編

どんどん行きます。

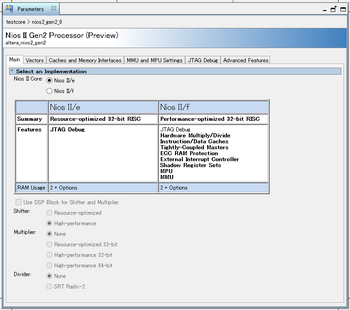

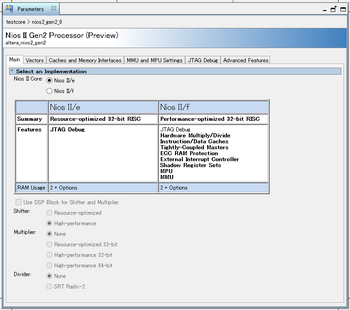

MAX10で新しくNiosIIのデザインをする場合は、旧来のNiosIIではなく、NiosII Gen2を使う必要があります。

→ 参照:MAX10でNiosII動かしてみた

NiosII Gen2では、/eコアと/fコアの2種類に整理されています。/eコアは無償で使えるフリー版で、/fコアは有償コアです。旧来の/sコアは/fコアの設定変更で/sコア相当の機能やフットプリントを選択できるような運用に変更されました。

また内部ロジックはMAX10への実装にあわせ、命令デコーダのテーブルをM9kメモリの初期値を使わないように変更されているようです(リセット動作時にプリロードしている?)。

Gen2ではこの他、割り込みやリセットのベクタを絶対アドレス指定でも行えるようになっています。フィッティングの効率やタイミング収束は旧来のコアとあまり変わりません。NiosII SBTの対応も変更はありません。

ちなみに、既に生成したQsysコンポーネントに含まれるNiosIIのデザインは、MAX10でもそのままコンパイルすることができます。

MAX10で新しくQsysコンポーネントをデザインする場合のみ、Gen2が必要になるわけです。ただ、当然ながらGen2でないNiosIIでは初期値付きのM9kメモリマクロを使っているため、ERAM Preloadのオプションを有効にしておかなければなりません(これの制限については後述)。

なお、MAX10では内蔵のUFM(ユーザーFlashメモリ領域)がAvalon-MMのメモリデバイスとしてマッピングされるため、NiosIIからはそのままROMとして使うことができます。

UFMの内容はコンフィグデータとは別にProgrammerで書き込むことが出来るため、QuartusIIで再コンパイルすることなくブートプログラム(あるいは小規模なアプリケーションなど)を差し替えられるようになり、ワンチップマイコンに近い運用ができるようになりました。

4.I/O編

MAX10のI/O機能はそれまでのデバイスのI/Oに比べるとかなり強化されていて、機能的にはCyclone VとMAX Vを足してさらにLVDSの差動入力を増やしたようなイメージになっています。

→ 参照:MAX 10 General Purpose I/O User Guide

→ 参照:MAX 10 High-Speed LVDS I/O User Guide

内部アーキテクチャが同等のCycloneIII/IV Eと比べてIOEがかなり改良されていて、ピンマッピングが使いやすくなっています。

個人的にSODALITEで10M08SAE144C8GESを使ってみてプラスポイントだったのが

もともとE144ではI/Oピンが限られていて、特に大規模のデバイスになるとクロックの入力専用ピンが、実運用上I/O数を相当数削ってしまっていたのですが、MAX10ではCLKピンがI/Oとして使えるようになったためI/Oに余裕が出ました。これだけでもかなりありがたい。

また、これまでVREFピンにはIOレジスタがなかったので、SDRAMなどの高速パラレル信号を配置するとデータスキューが頭の痛い問題になっていました(例:DE0のDRAM_WE_NとDRAM_DQ3)が、MAX10ではVREFピンにもIOレジスタが追加されて、他のI/Oピンとデータスキューがきれいに揃うようになっています。

そんなわけでSODALITEではSDRAMのピンアサインをBANK4~BANK7のI/Oピンを片っ端から全部割り当ててピン数を稼ぐことができてます。

その他、高速系の電気規格についてもBusLVDSや、SLVS、TMDSなどに新たに対応していて、さらにほぼ全ピンに差動入力ペアが設定されており、これまでの廉価FPGAよりもさらに高速シリアル信号のインターフェースを強化してきた印象を受けます。

5.ADC編

さてMAX10の目玉。新しく追加されたアナログ機能です。

→ 参照:MAX 10 アナログ-デジタル・コンバータ・ユーザー・ガイド

MAX10ではALTERAデバイスとしては初めてADCを内蔵しています。

10M08SAE144では10:1のアナログマルチプレクサを搭載し、外部9チャネル+内蔵温度を、最大1Msps、12bit精度の分解能でサンプリングすることができます。

またリファレンス電圧も内部生成のほか外部からの入力にも対応していて、より高精度のA/D変換ができるようになっています。

ただ、現時点(14.0 Update2)ではADC機能モジュールはQsysのAvalonコンポーネントのβ版のみとなっていて、IP Catalogからはインスタンスできないので、使いどころが限られています。あとIPコア自体もまだ使いにくい。

ここはQuarutsII 14.1の正式対応を待ちましょう。

で、ここまでいろいろと機能たくさんのMAX10ですが、当然ながら諸手を挙げて万事OKかというとそうでもなくて、機能毎の排他的な制約がいろいろと付いてくるわけです。

なによりもADCを使った時の制限がなかなかシャレにならず、ものによっては致命的なインパクトになりうる場合があります。

次回エントリではMAX10の制限についてまとめます。

MAX10はラインナップ上いくつかのバリエーションがあるものの、ここでは全部網羅することはできないので、MAX10 evalボードおよびSODALITE基板で採用の10M08SAE144C8GESに限って話をすすめることにします。それ以外のデバイスについては適宜データシートを参照のこと。

→ オンライン資料:MAX 10 FPGA

1.コンパイル編

まずQuartusIIでのコンパイルから。

MAX10はまだQuartusIIでは正式に対応している状態ではなく、14.0のアップデートパッチ(Update2)による暫定対応となっています(正式対応は14.1で、これは来週のALTERAサーバーメンテ開けにリリースされるものと思われる)。

→ 参照:MAX10ボードがもうすぐ到着

QuartusII 14.0をインストール後、Update2パッチをインストールすることでMAX10デバイスが選択できるようになります。また14.0 Update2ではラインナップのうち、10M02/10M04/10M08と10M40および50がライブラリとして用意されており、まだ全ラインナップが揃っていません。

次にコンパイルに関しても、MAX10では既存のFPGAデバイスとはくせの違う部分があります。

大きな差の一つが、メモリマクロの初期値についての問題で、MAX10デバイスで初期値付きのメモリを使う場合は Settings→Analysys&Synthesis→More Settings で追加設定を開き、その中のEnable ERAM PreloadをOff→Onにします。

→ 参照:MAX 10 エンベデッド・メモリ・ユーザーガイド(4-6 注釈)

2.書き込み編

続いてデバイスへのダウンロード。

14.0 Update2ではSOFまでしか生成されず、POFは手動で生成してやる必要があります。

→ 参照:MAX10ボード使ってみた

ここで注意しないといけないのは、MAX10では(少なくとも現段階では)何もコンフィグレーションされてない状態ではPOFの書き込みが出来ない点です。これはかなりハマりました‥‥。

なので、予め何らかのSOFをダウンロードしてMAX10デバイス内部をコンフィグレーションさせておく必要があります。

MAX10 evalボードでは最初にテストコンフィグが入っていますが、デバイスイレースをすると未コンフィグ状態になるので注意が必要です。

またもう一つ、MAX10デバイスのES品では出荷時にリコンフィグレーション・タイムアウト機能が有効になっていて、何も書き込まずにSOFだけダウンロードしていると勝手にリコンフィグします。傍目にはブラウンアウトリセットがかかったように見えるのでタチが悪い‥‥。

リコンフィグレーション・タイムアウト機能の解除の仕方はErrata Sheet and Guidelines for MAX 10 ES Devices (英語版・PDF)の最後に記載がありますが

の操作が必要です。

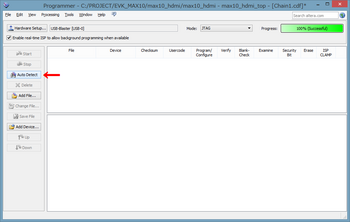

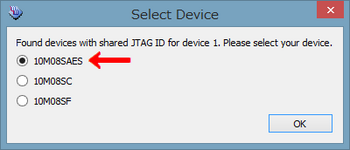

- Programmerを起動

- AutoDetectでデバイスを選択

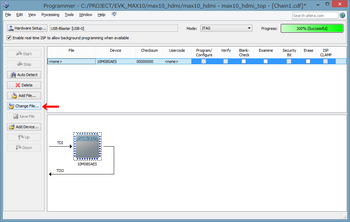

- Eraseにチェックを入れる

- Startボタンをクリック

- 再度電源を入れ直す

イレースしただけではタイムアウト機能はそのままなので、いったん電源を入れ直してデバイス内部を初期化し直す必要があります。

このリコンフィグレーション・タイムアウト機能のやっかいなところは、POFの書き込みにかかる時間よりもタイムアウト時間の方が短いため、最初にこの機能をOFFにしとかないとPOFの書き込みが途中で失敗する(勝手にリコンフィグする)ことです。これまただいぶハマった‥‥。

ところで、うちの環境ではUSB-Blaster Rev.Bの接続で、MAX10 evalボードでもSODALITEボードでもJTAGのリンクが頻繁に切れるという問題が発生してます。

レベル変換を省いてMAX3000A直結のクローンBlasterでは問題が出てないあたり、どうもUSB-Blaster Rev.Bの電気仕様とMAX10のJTAGピンの電気仕様の相性がよろしくないのかもしれません。

単にうちのUSB-Blasterが死にかけなだけかもしれませんが、まあそういう事例も出てますということで。

3.NiosII編

どんどん行きます。

MAX10で新しくNiosIIのデザインをする場合は、旧来のNiosIIではなく、NiosII Gen2を使う必要があります。

→ 参照:MAX10でNiosII動かしてみた

NiosII Gen2では、/eコアと/fコアの2種類に整理されています。/eコアは無償で使えるフリー版で、/fコアは有償コアです。旧来の/sコアは/fコアの設定変更で/sコア相当の機能やフットプリントを選択できるような運用に変更されました。

また内部ロジックはMAX10への実装にあわせ、命令デコーダのテーブルをM9kメモリの初期値を使わないように変更されているようです(リセット動作時にプリロードしている?)。

Gen2ではこの他、割り込みやリセットのベクタを絶対アドレス指定でも行えるようになっています。フィッティングの効率やタイミング収束は旧来のコアとあまり変わりません。NiosII SBTの対応も変更はありません。

ちなみに、既に生成したQsysコンポーネントに含まれるNiosIIのデザインは、MAX10でもそのままコンパイルすることができます。

MAX10で新しくQsysコンポーネントをデザインする場合のみ、Gen2が必要になるわけです。ただ、当然ながらGen2でないNiosIIでは初期値付きのM9kメモリマクロを使っているため、ERAM Preloadのオプションを有効にしておかなければなりません(これの制限については後述)。

なお、MAX10では内蔵のUFM(ユーザーFlashメモリ領域)がAvalon-MMのメモリデバイスとしてマッピングされるため、NiosIIからはそのままROMとして使うことができます。

UFMの内容はコンフィグデータとは別にProgrammerで書き込むことが出来るため、QuartusIIで再コンパイルすることなくブートプログラム(あるいは小規模なアプリケーションなど)を差し替えられるようになり、ワンチップマイコンに近い運用ができるようになりました。

4.I/O編

MAX10のI/O機能はそれまでのデバイスのI/Oに比べるとかなり強化されていて、機能的にはCyclone VとMAX Vを足してさらにLVDSの差動入力を増やしたようなイメージになっています。

→ 参照:MAX 10 General Purpose I/O User Guide

→ 参照:MAX 10 High-Speed LVDS I/O User Guide

内部アーキテクチャが同等のCycloneIII/IV Eと比べてIOEがかなり改良されていて、ピンマッピングが使いやすくなっています。

個人的にSODALITEで10M08SAE144C8GESを使ってみてプラスポイントだったのが

このうち上2つはI/O機能とは直接関係ないので置いとくとして、下2つがかなり良くなっています。

- 3.3Vまたは3.0Vの単電源で動く

- 低消費電力(~0.5W)

- VREFピンにもIOレジスタが割り当てられた

- CLKピンが通常のI/Oピンとしても使えるようになった

もともとE144ではI/Oピンが限られていて、特に大規模のデバイスになるとクロックの入力専用ピンが、実運用上I/O数を相当数削ってしまっていたのですが、MAX10ではCLKピンがI/Oとして使えるようになったためI/Oに余裕が出ました。これだけでもかなりありがたい。

また、これまでVREFピンにはIOレジスタがなかったので、SDRAMなどの高速パラレル信号を配置するとデータスキューが頭の痛い問題になっていました(例:DE0のDRAM_WE_NとDRAM_DQ3)が、MAX10ではVREFピンにもIOレジスタが追加されて、他のI/Oピンとデータスキューがきれいに揃うようになっています。

そんなわけでSODALITEではSDRAMのピンアサインをBANK4~BANK7のI/Oピンを片っ端から全部割り当ててピン数を稼ぐことができてます。

その他、高速系の電気規格についてもBusLVDSや、SLVS、TMDSなどに新たに対応していて、さらにほぼ全ピンに差動入力ペアが設定されており、これまでの廉価FPGAよりもさらに高速シリアル信号のインターフェースを強化してきた印象を受けます。

5.ADC編

さてMAX10の目玉。新しく追加されたアナログ機能です。

→ 参照:MAX 10 アナログ-デジタル・コンバータ・ユーザー・ガイド

MAX10ではALTERAデバイスとしては初めてADCを内蔵しています。

10M08SAE144では10:1のアナログマルチプレクサを搭載し、外部9チャネル+内蔵温度を、最大1Msps、12bit精度の分解能でサンプリングすることができます。

またリファレンス電圧も内部生成のほか外部からの入力にも対応していて、より高精度のA/D変換ができるようになっています。

ただ、現時点(14.0 Update2)ではADC機能モジュールはQsysのAvalonコンポーネントのβ版のみとなっていて、IP Catalogからはインスタンスできないので、使いどころが限られています。あとIPコア自体もまだ使いにくい。

ここはQuarutsII 14.1の正式対応を待ちましょう。

で、ここまでいろいろと機能たくさんのMAX10ですが、当然ながら諸手を挙げて万事OKかというとそうでもなくて、機能毎の排他的な制約がいろいろと付いてくるわけです。

なによりもADCを使った時の制限がなかなかシャレにならず、ものによっては致命的なインパクトになりうる場合があります。

次回エントリではMAX10の制限についてまとめます。

2014-11-19 03:51

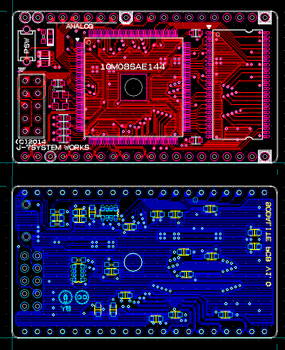

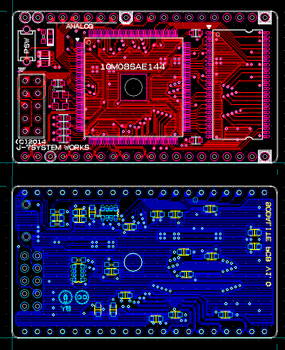

MAX10ボードできた [FPGA]

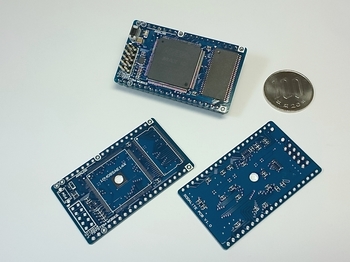

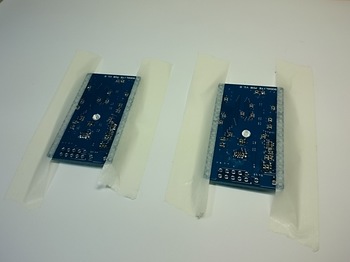

前回のエントリで発注したMAX10基板(SODALITE)ができあがってきたので早速実装してテスト。

小型の基板で、かつ両サイドに貫通部品の穴が開いてるので、マスキングテープでケント紙に固定してハンダ付け。

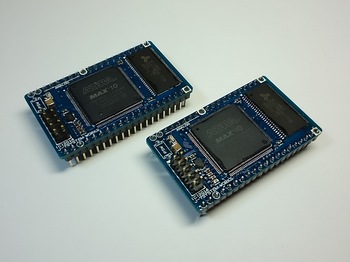

実装完了。

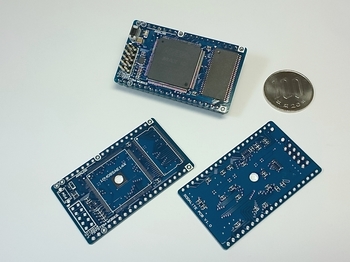

サイズはこんな感じで実にコンパクト。

MILピッチコネクタで外部にI/Oを引きだしているので、ユニバーサル基板で組めます。

早速HDMIで表示させてみた。

MAX10 evalボードではテストしてなかった720p解像度(1レーン742.5Mbps)を出してみたところ。シリアライザは372MHzで動作している。CycloneIV EのC8グレードではこのスピードをLVDSで作ると弾かれるんだけども、MAX10のC8グレードは問題ないようだ。

こないだあれだけ苦労したSDRAMも何ら問題無く動作して、これでようやく1ヶ月前の評価をし直せる状態に戻った。これから消費電力とか温度特性とか調べていきます。

教訓:新しいデバイスやメモリバスは信頼できるボードを先に買え

MAX10デバイスを使ってみていろいろ分かってきたことは次回のエントリで

→ MAX10デバイスを使う場合の注意まとめ(その1)

小型の基板で、かつ両サイドに貫通部品の穴が開いてるので、マスキングテープでケント紙に固定してハンダ付け。

実装完了。

サイズはこんな感じで実にコンパクト。

MILピッチコネクタで外部にI/Oを引きだしているので、ユニバーサル基板で組めます。

早速HDMIで表示させてみた。

MAX10 evalボードではテストしてなかった720p解像度(1レーン742.5Mbps)を出してみたところ。シリアライザは372MHzで動作している。CycloneIV EのC8グレードではこのスピードをLVDSで作ると弾かれるんだけども、MAX10のC8グレードは問題ないようだ。

こないだあれだけ苦労したSDRAMも何ら問題無く動作して、これでようやく1ヶ月前の評価をし直せる状態に戻った。これから消費電力とか温度特性とか調べていきます。

教訓:新しいデバイスやメモリバスは信頼できるボードを先に買え

MAX10デバイスを使ってみていろいろ分かってきたことは次回のエントリで

→ MAX10デバイスを使う場合の注意まとめ(その1)

2014-11-18 04:54

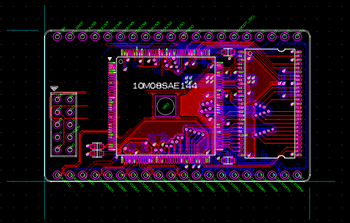

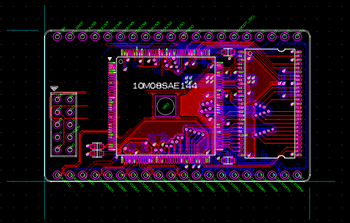

新MAX10ボード製作中 [FPGA]

MAX10_evalボードの限界が見えてしまったので(特にSDRAM接続まわりで)、新ボードを起こすことにした。

似たようなコンセプトのボードがマクニカから出ることは知っていたので、こちらはまぁテスト用にぐらいの気持ちでいたら、SDRAMが載ってないことがわかり、手持ちのリソースでなんとかしないといけない羽目に。

そんなわけで、久々の鉱物シリーズ基板(コードネームが鉱物の基板)を企画。

主な特徴は

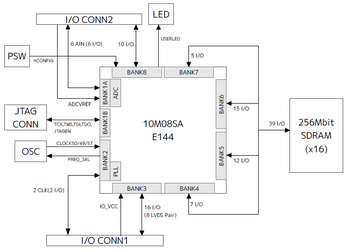

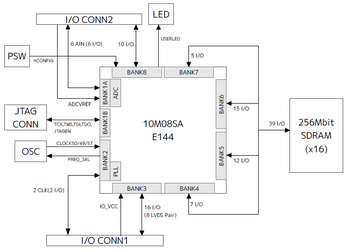

ブロック図

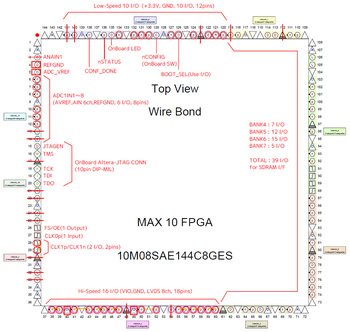

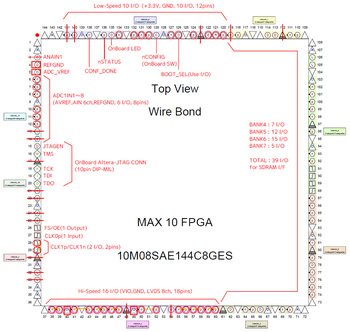

10M08SAE144のピン割り振り

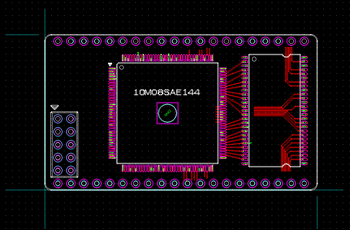

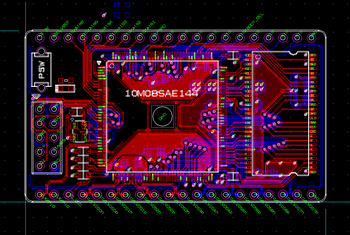

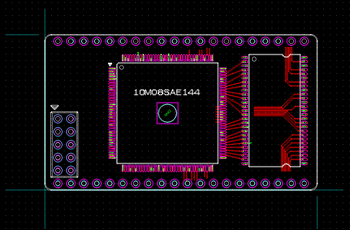

そんなわけでアートワーク開始。

まずはおおまかに配置を決める。

今回は面積最優先なのと、ほとんどがピン-ピンの接続であること、相手がMAX10だと電源とJTAGとコンフィグピンさえ間違わなければ、あとからいくらでもリカバリ可能なことから、回路図レスでいきなりアートワークから始めてる。当然ながら素人にも玄人にもおすすめできない。

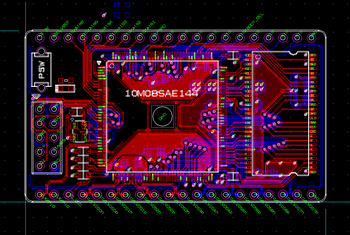

SDRAMまわりの配線を追い込む。

このへんからで電源の配線との戦い。

2層基板の場合では、電源と配線のプレーンが満足に取れないので、とれぐらいましな構成にできるかがアートワークの善し悪しになる。

ちなみに、FPGAみたいにほとんどが汎用信号ピンにできるデバイスでは、部品面を配線にしてハンダ面をベタGNDにしていくのが一番マシなアートワークにできる。

電源ピンは多少引き回してもパスコンの配置で逃げようがあるが、GNDピンはそういう手段がとれないので、とにかく裏面を可能な限りベタにして「入り江」や「島」を作らないことを第一に考えてる。

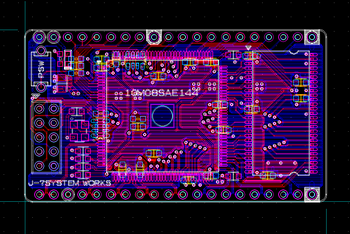

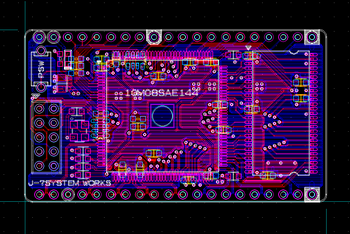

そんなわけでアートワーク完成\(^o^)/

配線チェック(拡大印刷とカラーマーカーの出番)してシルクを入れ、基板屋さんに発注。

ちなみに今回はドリルのアニュラリングとラインスペースをギリギリまで削ってるので、格安基板は使わず安心のP板.com

デザインルールは当然確認しているが、工場の特性をきちんと把握しているところで最終チェックをしてもらわないと、乗っかる部品が高価なだけにあとで泣きをみる。

到着までに部品も発注。

似たようなコンセプトのボードがマクニカから出ることは知っていたので、こちらはまぁテスト用にぐらいの気持ちでいたら、SDRAMが載ってないことがわかり、手持ちのリソースでなんとかしないといけない羽目に。

そんなわけで、久々の鉱物シリーズ基板(コードネームが鉱物の基板)を企画。

主な特徴は

1100mil幅40ピンDIP基板(基板サイズ53.4mm×30.5mm)

10M08SAE144C8N搭載

256Mbit SDRAM(x16幅,最大143MHz)搭載

周波数切り替え可能なOSC(50.0MHz/24.576MHz/74.25MHz)搭載

PIO最大34本(アナログ6チャネル、LVDS 8チャネル)

3.3V単一電源駆動

ADC用VREFおよびIO_VCCの外部入力可能

ブロック図

10M08SAE144のピン割り振り

そんなわけでアートワーク開始。

まずはおおまかに配置を決める。

今回は面積最優先なのと、ほとんどがピン-ピンの接続であること、相手がMAX10だと電源とJTAGとコンフィグピンさえ間違わなければ、あとからいくらでもリカバリ可能なことから、回路図レスでいきなりアートワークから始めてる。当然ながら素人にも玄人にもおすすめできない。

SDRAMまわりの配線を追い込む。

このへんからで電源の配線との戦い。

2層基板の場合では、電源と配線のプレーンが満足に取れないので、とれぐらいましな構成にできるかがアートワークの善し悪しになる。

ちなみに、FPGAみたいにほとんどが汎用信号ピンにできるデバイスでは、部品面を配線にしてハンダ面をベタGNDにしていくのが一番マシなアートワークにできる。

電源ピンは多少引き回してもパスコンの配置で逃げようがあるが、GNDピンはそういう手段がとれないので、とにかく裏面を可能な限りベタにして「入り江」や「島」を作らないことを第一に考えてる。

そんなわけでアートワーク完成\(^o^)/

配線チェック(拡大印刷とカラーマーカーの出番)してシルクを入れ、基板屋さんに発注。

ちなみに今回はドリルのアニュラリングとラインスペースをギリギリまで削ってるので、格安基板は使わず安心のP板.com

デザインルールは当然確認しているが、工場の特性をきちんと把握しているところで最終チェックをしてもらわないと、乗っかる部品が高価なだけにあとで泣きをみる。

到着までに部品も発注。

2014-11-10 11:01

MAX10ボードがそろそろ限界 [FPGA]

いろいろといじくり倒したMAX10ボードだけども、そろそろ限界が見えてきた感じ。

表はあんまりいじってないけど、裏側はこんな状態

micoSDカードスロットとSDRAMを余ってるピンに配置したのだけども、NiosIIの時にキャッシュが上手く動かなかったのはどうやらSDRAMのデータ線の信号品質がギリギリアウトの領域に入ってた模様。

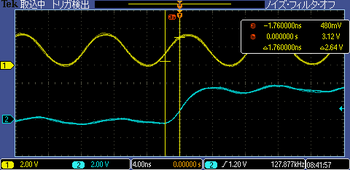

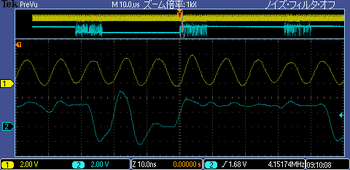

オシロでクロックラインとDQを見てみるが‥‥

100MHzの信号は帯域200MHzのオシロじゃ分からん!ヽ(`口´)ノ

VGAの出力が綺麗に出ていること、NiosII/eではmicroSDカードの読み出しがきちんと動作すること、NiosII/sや/fにするとデータキャッシュが無くても途中でハングアップすること、などから察するに、おそらく書き込み方向のバーストアクセスが問題だろうと予想している。

バースト読み出しが問題ならVGAの表示がおかしくなるはずだし、書き込みが全部問題ならNiosII/eでも問題が出てるはずだ。VGAやNiosII/eに無くて、NiosII/sや/fが持っている特徴といえば、全段パイプラインによるメモリへのバーストアクセスだからだ。

というわけで、MAX10ボードでできることはそろそろ限界になりつつある。ボード起こそう。

DMM.make AKIBAで測定とか実装とかできませんかね?

表はあんまりいじってないけど、裏側はこんな状態

micoSDカードスロットとSDRAMを余ってるピンに配置したのだけども、NiosIIの時にキャッシュが上手く動かなかったのはどうやらSDRAMのデータ線の信号品質がギリギリアウトの領域に入ってた模様。

オシロでクロックラインとDQを見てみるが‥‥

100MHzの信号は帯域200MHzのオシロじゃ分からん!ヽ(`口´)ノ

VGAの出力が綺麗に出ていること、NiosII/eではmicroSDカードの読み出しがきちんと動作すること、NiosII/sや/fにするとデータキャッシュが無くても途中でハングアップすること、などから察するに、おそらく書き込み方向のバーストアクセスが問題だろうと予想している。

バースト読み出しが問題ならVGAの表示がおかしくなるはずだし、書き込みが全部問題ならNiosII/eでも問題が出てるはずだ。VGAやNiosII/eに無くて、NiosII/sや/fが持っている特徴といえば、全段パイプラインによるメモリへのバーストアクセスだからだ。

というわけで、MAX10ボードでできることはそろそろ限界になりつつある。ボード起こそう。

DMM.make AKIBAで測定とか実装とかできませんかね?

2014-11-01 06:38

MAX10でファミマチャイム [FPGA]

作業の合間にちょろっと作ってみた

Githubのリポジトリはこちら

→ https://github.com/osafune/max10_famimachime

ちなみに和音やエンベローブもすべてロジックで計算している。フルロジックで使用リソースは255LEしか使ってないので、ロジックの片隅に入れておくチャイムとしては使い道があるかも。

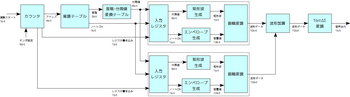

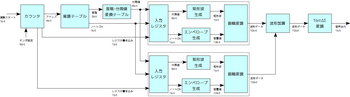

全体のブロック図がこれ

2個の音源(矩形波+エンベローブ)に対して、音譜テーブルでノートを発行している。

それより後は、矩形波のみ2ポリフォニックの音源の構成で、実は音源コアの基本中の基本構成。

この波形生成部分のデューティー比を調整できるようにしたのがPSG音源で、波形のパターンを選べるようになったのがSSG音源。さらに、ごく短い波形をループ再生するようにしたのがWSG音源というわけ。

いろいろ改造してみるといいかも。

Githubのリポジトリはこちら

→ https://github.com/osafune/max10_famimachime

ちなみに和音やエンベローブもすべてロジックで計算している。フルロジックで使用リソースは255LEしか使ってないので、ロジックの片隅に入れておくチャイムとしては使い道があるかも。

全体のブロック図がこれ

2個の音源(矩形波+エンベローブ)に対して、音譜テーブルでノートを発行している。

それより後は、矩形波のみ2ポリフォニックの音源の構成で、実は音源コアの基本中の基本構成。

この波形生成部分のデューティー比を調整できるようにしたのがPSG音源で、波形のパターンを選べるようになったのがSSG音源。さらに、ごく短い波形をループ再生するようにしたのがWSG音源というわけ。

いろいろ改造してみるといいかも。

2014-10-21 00:26

MAX10でNiosII動かしてみた(追記あり) [FPGA]

連休中は台風19号接近のため、予定していた九州慰安旅行がキャンセルになってしまいました。

なので、ずっとMAX10ボードをいじっていたわけですが。

前回で書き込みファイルはできるようになったので、今回はNiosIIをMAX10で動かしてみます。

QuartusIIでプロジェクトを作成してQsysでコンポーネントを追加するのはそのままですが、MAX10では旧来のNiosIIはサポートされていないので、Gen2をインスタンスする必要があります。

NiosII Gen2では、コアの種別が/eコアと/fコアの2種類になりました。

これまでの/sコアはどうなったのかというと、/fコアのカスタマイズで/sコア相当のものが作れるようになっています。

逆にこれまでできなかった、/sコアにあとデータキャッシュだけ欲しい、という細かい設定が可能になりました。

/fコア自体も、ECCメモリによるエラー保護や高速割り込みに対応したシャドウレジスタ機能など、細かいアップデートが施されています。

また、Gen2ではメモリタイプのペリフェラルに紐付けされていたベクタアドレスを、絶対値アドレスで設定できるようになりました。

Qsysでは生成したコンポーネントをさらにQsysで再利用できますが、これまでNiosIIを内蔵したコンポーネントではペリフェラル名のオフセットでベクタが指定されてしまうため、プログラムを外部に置くようなシステムコンポーネントが作りづらかったのが、独立したMPUとしても扱えるようになりました。

そんなNiosII Gen2ですが、実際の使い勝手は旧来のNiosIIとまったく同じです。

いつもの通り、100MHzのシステムクロックと、40MHzのペリフェラルクロックを生成して、NiosIIコアと内蔵メモリとペリフェラルを生成します。

ペリフェラルはいつもの通り、sysid、timer、jtag-uart、それからLEDとDIPスイッチを読むIN/OUTのPIOと、MAX10 EVKボード上のArduinoシールドコネクタピンに直結しているBidir-PIOをつけました。

ペリフェラルアクセスにはクロックドメインを跨ぐ必要がありますが、Avalon-MM Pipeline Bridge でまとめてペリフェラルクロックへドメインをまとめます(ちなみに Avalon-MM Clock Crossing Bridge を使わないのは、ペリフェラル側はバーストアクセス不要なのでLEをケチるため)。

途中いろいろすっ飛ばしてLチカをしてみたのがこちら

さらに途中をすっ飛ばして、SDRAMコントローラとVGAコンポーネントを追加してHDMIに絵を出してみたのがこちら

なので、ずっとMAX10ボードをいじっていたわけですが。

前回で書き込みファイルはできるようになったので、今回はNiosIIをMAX10で動かしてみます。

QuartusIIでプロジェクトを作成してQsysでコンポーネントを追加するのはそのままですが、MAX10では旧来のNiosIIはサポートされていないので、Gen2をインスタンスする必要があります。

NiosII Gen2では、コアの種別が/eコアと/fコアの2種類になりました。

これまでの/sコアはどうなったのかというと、/fコアのカスタマイズで/sコア相当のものが作れるようになっています。

逆にこれまでできなかった、/sコアにあとデータキャッシュだけ欲しい、という細かい設定が可能になりました。

/fコア自体も、ECCメモリによるエラー保護や高速割り込みに対応したシャドウレジスタ機能など、細かいアップデートが施されています。

また、Gen2ではメモリタイプのペリフェラルに紐付けされていたベクタアドレスを、絶対値アドレスで設定できるようになりました。

Qsysでは生成したコンポーネントをさらにQsysで再利用できますが、これまでNiosIIを内蔵したコンポーネントではペリフェラル名のオフセットでベクタが指定されてしまうため、プログラムを外部に置くようなシステムコンポーネントが作りづらかったのが、独立したMPUとしても扱えるようになりました。

(追記)>‥‥と書いててなんですが、どうもNiosII Gen2 /fコアのデータキャッシュを使うと、IORD/IOWRによるマクロが上手く動作しないようです。特にIORDでのレジスタポーリングが致命的で、コンパイラはldwio命令を生成しているものの、挙動を見る限りデータキャッシュがバイパスされていない模様です。

どうやら基板裏に実装したSDRAMのバーストアクセスでごくまれにリードミスを起こしている模様。ロジックのせいではないようです。 → MAX10ボードがそろそろ限界(2014-11-01)

そんなNiosII Gen2ですが、実際の使い勝手は旧来のNiosIIとまったく同じです。

いつもの通り、100MHzのシステムクロックと、40MHzのペリフェラルクロックを生成して、NiosIIコアと内蔵メモリとペリフェラルを生成します。

ペリフェラルはいつもの通り、sysid、timer、jtag-uart、それからLEDとDIPスイッチを読むIN/OUTのPIOと、MAX10 EVKボード上のArduinoシールドコネクタピンに直結しているBidir-PIOをつけました。

ペリフェラルアクセスにはクロックドメインを跨ぐ必要がありますが、Avalon-MM Pipeline Bridge でまとめてペリフェラルクロックへドメインをまとめます(ちなみに Avalon-MM Clock Crossing Bridge を使わないのは、ペリフェラル側はバーストアクセス不要なのでLEをケチるため)。

途中いろいろすっ飛ばしてLチカをしてみたのがこちら

s_osafuneMAX10でLチカできたよー http://t.co/PyWFrCT3nK10/12 18:15

さらに途中をすっ飛ばして、SDRAMコントローラとVGAコンポーネントを追加してHDMIに絵を出してみたのがこちら

s_osafuneMAX10でSDRAMコントローラとVGAコンポーネント動いたよー http://t.co/qHHgmqbjwi10/12 22:49

2014-10-14 11:11

MAX10ボード使ってみた [FPGA]

MAX10ボードが到着したので早速いろいろ試してみた。

QuartusII 14.0 Update2は、まだ即席対応で、とってつけた感が否めない。

前回エントリのRAM初期値オプションもさることながら、14.0 Update2ではまだPOFが自動生成されない。

なので、スタンドアロンで動かす場合はPOFを手作業で作成する必要がある。

MAX10では単体コンフィグのシングルコンフィギュレーションと、2つのコンフィグデータを格納するデュアルコンフィギュレーションの2つのコンフィグモードを使うことができるが、今回はシングルコンフィギュレーション用のデータを作成する。

まずQuartusIIでMAX10用のプロジェクトをコンパイルする。

次に、File→Convert Programming files...を選択して、コンバートツールを起動する。

Modeプルダウンメニューから「Internal configuration」を選択。

File nameで出力先のファイル名を指定する。

Input files to convertのSOF Dataを選択して、Add File..をクリック。

QuartusIIで生成したsofファイルを選択。

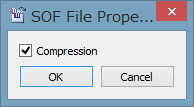

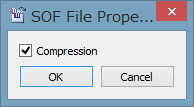

読み込まれたsofを選択して、Propertiesをクリック。

CompressionにチェックをいれてOKをクリック。

Generateをクリックするとpofファイルが生成される。

Closeでコンバートツールを終了させて、次にQuartusII Programmerを呼び出す。

ボードにUSB-Blasterを接続してAuto Detectをクリックする。

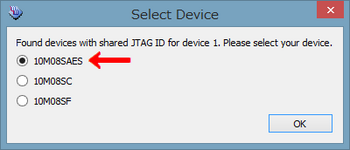

「10M08SAES」を選択してOKをクリック。

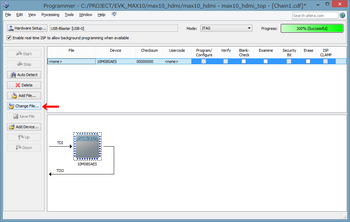

デバイスを選択して、Change File...をクリック。

先ほど生成したpofファイルを選択。

Program/Configureの一番上のチェックボックスにチェックを入れるとCFMとUFMにもチェックが入る。

StartをクリックするとMAX10デバイスにコンフィグレーションデータを書き込む。

結構時間がかかる。

プログレスバーが100%まで伸びてSuccessfulの表示が出たら書き込み完了。

ボード上のnCONFIGキー(SW2)を押すか、電源を入れ直すとMAX10が再コンフィグする。

さくっとHDMIコアをいれてテストパターンを表示させてみた。

NiosIIでLチカしてみた。

QuartusII 14.0 Update2は、まだ即席対応で、とってつけた感が否めない。

前回エントリのRAM初期値オプションもさることながら、14.0 Update2ではまだPOFが自動生成されない。

なので、スタンドアロンで動かす場合はPOFを手作業で作成する必要がある。

MAX10では単体コンフィグのシングルコンフィギュレーションと、2つのコンフィグデータを格納するデュアルコンフィギュレーションの2つのコンフィグモードを使うことができるが、今回はシングルコンフィギュレーション用のデータを作成する。

まずQuartusIIでMAX10用のプロジェクトをコンパイルする。

次に、File→Convert Programming files...を選択して、コンバートツールを起動する。

Modeプルダウンメニューから「Internal configuration」を選択。

File nameで出力先のファイル名を指定する。

Input files to convertのSOF Dataを選択して、Add File..をクリック。

QuartusIIで生成したsofファイルを選択。

読み込まれたsofを選択して、Propertiesをクリック。

CompressionにチェックをいれてOKをクリック。

Generateをクリックするとpofファイルが生成される。

Closeでコンバートツールを終了させて、次にQuartusII Programmerを呼び出す。

ボードにUSB-Blasterを接続してAuto Detectをクリックする。

「10M08SAES」を選択してOKをクリック。

デバイスを選択して、Change File...をクリック。

先ほど生成したpofファイルを選択。

Program/Configureの一番上のチェックボックスにチェックを入れるとCFMとUFMにもチェックが入る。

StartをクリックするとMAX10デバイスにコンフィグレーションデータを書き込む。

結構時間がかかる。

プログレスバーが100%まで伸びてSuccessfulの表示が出たら書き込み完了。

ボード上のnCONFIGキー(SW2)を押すか、電源を入れ直すとMAX10が再コンフィグする。

さくっとHDMIコアをいれてテストパターンを表示させてみた。

s_osafuneMAX10でHDMI映ったよー http://t.co/qbmUVkdwiY10/12 14:23

NiosIIでLチカしてみた。

s_osafuneMAX10でLチカできたよー http://t.co/PyWFrCT3nK10/12 18:15

2014-10-12 16:03

MAX10ボードがもうすぐ到着 [FPGA]

昨日MAX10シリーズが発表になり、即日出荷が始まっています。

アルテラ、次世代の不揮発性 MAX 10 FPGA、およびMAX 10 FPGA 評価キットの提供開始を発表

EVAボードはALTERAを初め、Arrowやマクニカから4種類が発表され、DigikeyやMouserで取り扱いが始まりました。

早速、ALTERAのEK-10M08E144ES/Pを注文してみました。

さて、それと平行してMAX10の実デバイス向けにコンフィグレーションデータを用意します。

MAX10はコンフィグレーションROMが内蔵されているため、外部コンフィグはMAX II/VのようにJTAGのみです。

コンパイルはQuartusII 14.0にMAX10用ライブラリを追加するUpdate2を導入します。

ダウンロード・センター Quartus II ウェブ エディション

QuartusプロジェクトはCycloneIIIやCycloneIV Eのものがほぼそのまま流用できます。

EPCSペリフェラルを使っているものはSPI Flash扱いになりますが、リモートアップデートペリフェラルはMAX10の内蔵ROMと競合してしまうので修正が必要になります。

また、MAX10では256ピン以下のパッケージのデバイスではPLLが1個しか使えないため、PLLを2個以上使っているデザインはそのまま流用できません。CycloneIII/IV EではE144パッケージでも2個または4個のPLLが使えたので、ここは要注意です。

Qsysで新しくデザインをする時は、旧来のNiosIIでは生成することができず、新しくNiosII Gen2のコンポーネントに差し替える必要があります。

QuartusII 14.0 Update2では、後付けでMAX10のライブラリを追加してコンフィグレーションデータを生成するようにしたため、本来は自動で設定されるであろう項目をマニュアルで設定しなければなりません。

このうち、特にクリティカルなのがM9kメモリマクロの設定です。

Settings→Analysys&Synthesis→More Settings で追加設定を開き、その中のEnable ERAM PreloadをOff→Onにします。

どうやらMAX10ではコンフィグレーションデータ圧縮のためにメモリマクロの初期化を変更しているようで、この設定をしないと初期値データ(.mifや.hex)があるM9kメモリがコンパイルエラーになります。

また、14.0 Update2では合成結果がsofまでしか生成されません。

MAX10デバイスに書き込むpofファイルを生成するには、File→Convert Programming file でsofをpofに変換します。UFMに書き込むユーザーデータやDualコンフィグレーションのsofもここで一緒にpofにまとめます。

MAX 10 FPGA Configuration User Guideに詳しい手順が書いてありますが、14.0 Update2と一部食い違う部分があり、現状はあくまで暫定環境という扱いだと思います。

QuartusII 14.1ではこのあたりの面倒くさい手順もすっきりすると思います。

アルテラ、次世代の不揮発性 MAX 10 FPGA、およびMAX 10 FPGA 評価キットの提供開始を発表

EVAボードはALTERAを初め、Arrowやマクニカから4種類が発表され、DigikeyやMouserで取り扱いが始まりました。

早速、ALTERAのEK-10M08E144ES/Pを注文してみました。

さて、それと平行してMAX10の実デバイス向けにコンフィグレーションデータを用意します。

MAX10はコンフィグレーションROMが内蔵されているため、外部コンフィグはMAX II/VのようにJTAGのみです。

コンパイルはQuartusII 14.0にMAX10用ライブラリを追加するUpdate2を導入します。

ダウンロード・センター Quartus II ウェブ エディション

QuartusプロジェクトはCycloneIIIやCycloneIV Eのものがほぼそのまま流用できます。

EPCSペリフェラルを使っているものはSPI Flash扱いになりますが、リモートアップデートペリフェラルはMAX10の内蔵ROMと競合してしまうので修正が必要になります。

また、MAX10では256ピン以下のパッケージのデバイスではPLLが1個しか使えないため、PLLを2個以上使っているデザインはそのまま流用できません。CycloneIII/IV EではE144パッケージでも2個または4個のPLLが使えたので、ここは要注意です。

Qsysで新しくデザインをする時は、旧来のNiosIIでは生成することができず、新しくNiosII Gen2のコンポーネントに差し替える必要があります。

QuartusII 14.0 Update2では、後付けでMAX10のライブラリを追加してコンフィグレーションデータを生成するようにしたため、本来は自動で設定されるであろう項目をマニュアルで設定しなければなりません。

このうち、特にクリティカルなのがM9kメモリマクロの設定です。

Settings→Analysys&Synthesis→More Settings で追加設定を開き、その中のEnable ERAM PreloadをOff→Onにします。

どうやらMAX10ではコンフィグレーションデータ圧縮のためにメモリマクロの初期化を変更しているようで、この設定をしないと初期値データ(.mifや.hex)があるM9kメモリがコンパイルエラーになります。

また、14.0 Update2では合成結果がsofまでしか生成されません。

MAX10デバイスに書き込むpofファイルを生成するには、File→Convert Programming file でsofをpofに変換します。UFMに書き込むユーザーデータやDualコンフィグレーションのsofもここで一緒にpofにまとめます。

MAX 10 FPGA Configuration User Guideに詳しい手順が書いてありますが、14.0 Update2と一部食い違う部分があり、現状はあくまで暫定環境という扱いだと思います。

QuartusII 14.1ではこのあたりの面倒くさい手順もすっきりすると思います。

2014-10-02 06:19